CHAPTER 5 CLOCK GENERATOR

Preliminary User’s Manual U16846EJ1V0UD

98

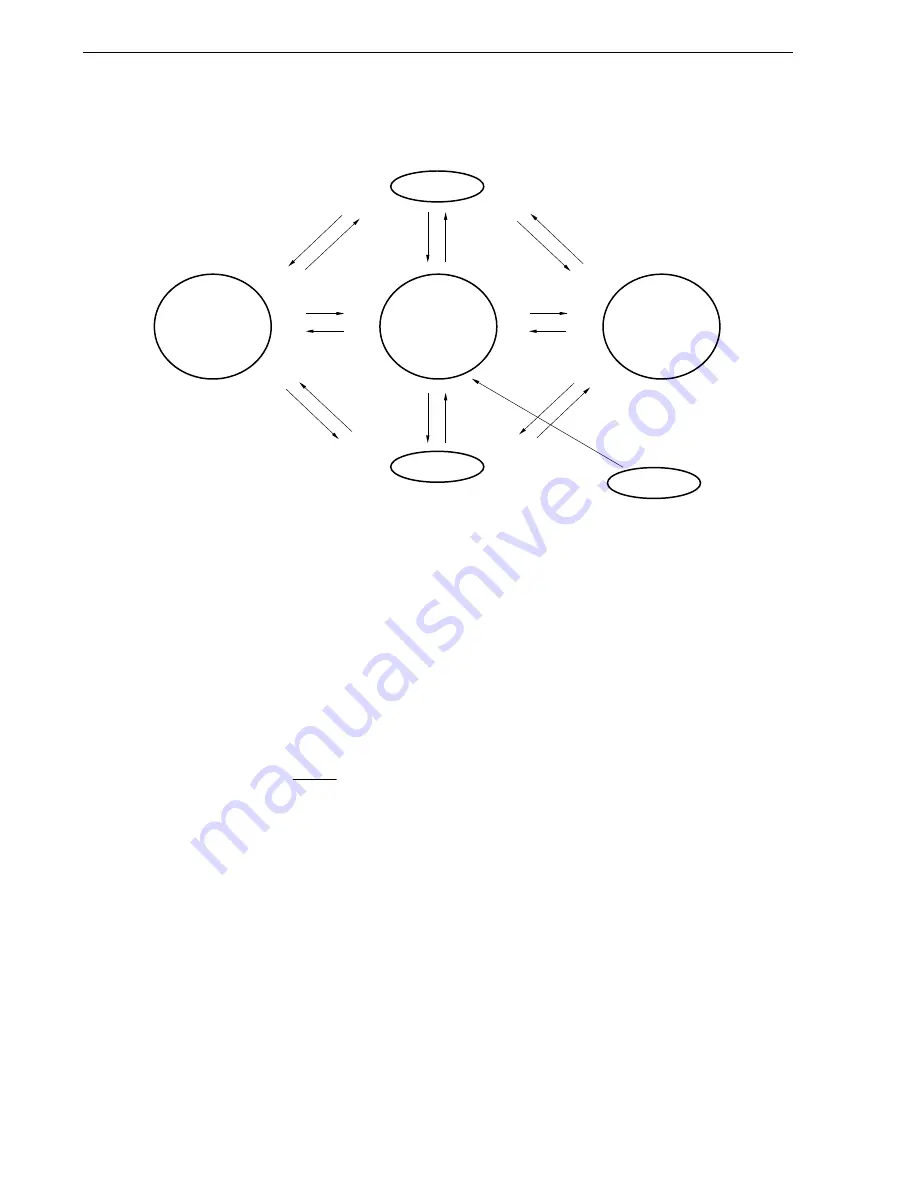

Figure 5-14. Status Transition Diagram (2/2)

(2) When “Ring-OSC cannot be stopped” is selected by option byte

Status 3

CPU clock: f

XP

f

XP

: Oscillating

f

R

: Oscillating

HALT

Interrupt

Interrupt

Interrupt

STOP

instruction

MCM0 = 0

MCM0 = 1

Note 1

HALT

instruction

HALT

instruction

STOP

Note 3

Reset

Note 4

Status 2

CPU clock: f

R

f

XP

: Oscillating

f

R

: Oscillating

Status 1

CPU clock: f

R

f

XP

: Oscillation stopped

f

R

: Oscillating

Interrupt

STOP

instruction

Interrupt

Interrupt

STOP

instruction

MSTOP = 1

Note 2

MSTOP = 0

HALT instruction

Reset release

Notes 1. Before shifting from status 2 to status 3 after reset and STOP are released, check the high-speed

system clock oscillation stabilization time status using the oscillation stabilization time counter status

register (OSTC).

Waiting for the oscillation stabilization time is not required when the external RC oscillation clock is

selected as the high-speed system clock by the option byte. Therefore, the CPU clock can be

switched without reading the OSTC value.

2. When shifting from status 2 to status 1, make sure that MCS is 0.

3. The watchdog timer operates using Ring-OSC even in STOP mode if “Ring-OSC cannot be stopped”

is selected by the option byte. Ring-OSC division can be selected as the count source of 8-bit timer

H1 (TMH1), so clear the watchdog timer using the TMH1 interrupt request before watchdog timer

overflow. If this processing is not performed, an internal reset signal is generated at watchdog timer

overflow after STOP instruction execution.

4. All reset sources (RESET input, POC, LVI, clock monitor, and WDT)