591

/

838

Nations Technologies Inc.

Tel

:

+86-755-86309900

:

Address: Nations Tower, #109 Baoshen Road, Hi-tech Park North.

Nanshan District, Shenzhen, 518057, P.R.China

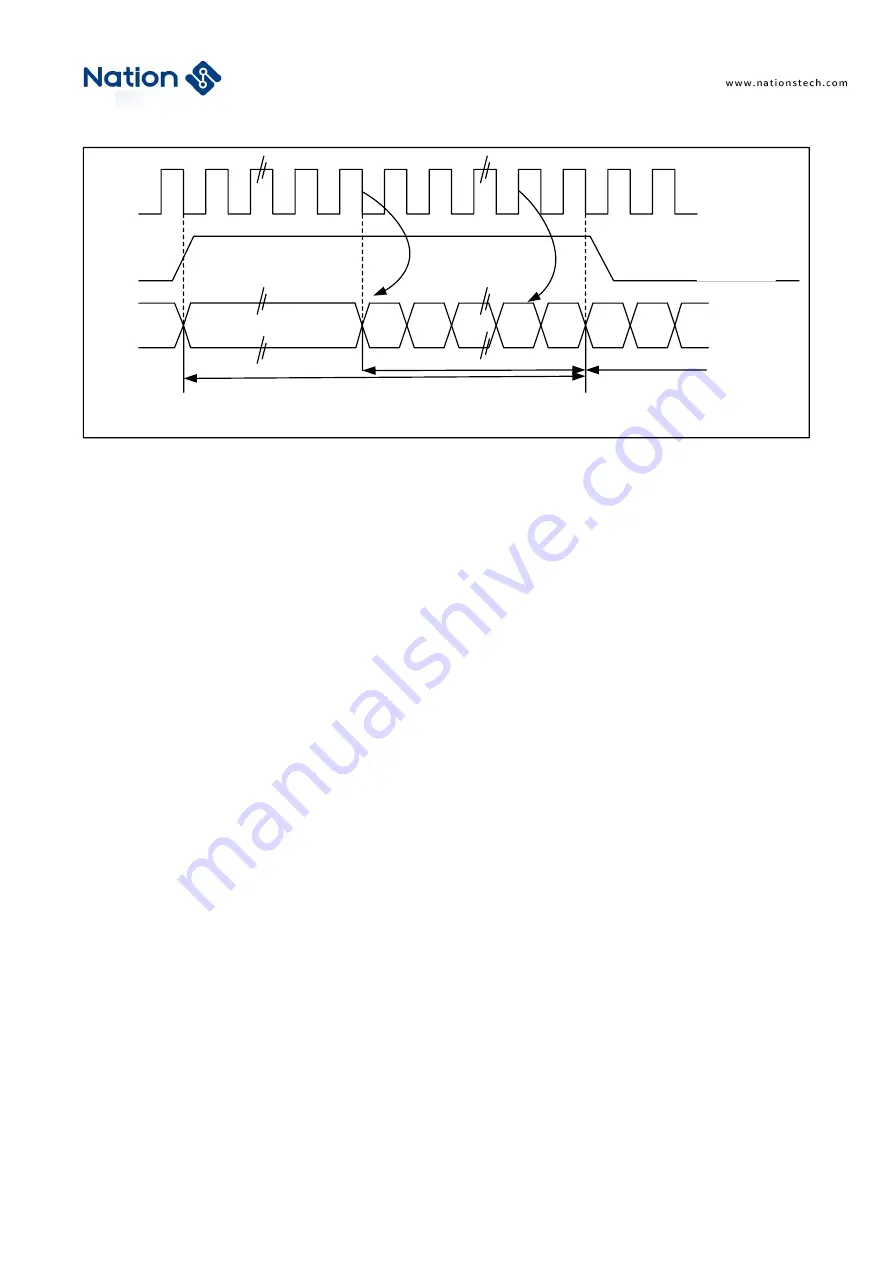

Figure 21-22 LSB aligned 16-bit data is extended to 32-bit packet frame, CLKPOL = 0

If the 16-bit data needs to be packaged into a 32-bit data frame format, the CPU only needs to read or write the

SPI_DAT register once for each frame of data transmission. The upper 16 bits of extended to 32 bits data are set to

0x0000 by hardware, if the user sends or receives 16-bit data 0x89C1 (extended to 32-bit data is 0x000089C1). In

the process of sending data, the upper 16-bit halfword (0x0000) needs to be written to the SPI_DAT register first;

once the valid data starts to be send, the next TE (SPI_STS.TE) event will be generated. In the process of receiving

data, once the device receives valid data, the RNE (SPI_STS.RNE) event will be generated. In this way, there is more

time between 2 reads and writes, which can prevent underflow or overflow from happening.

PCM standard

In the PCM standard, there are two frame structures, short frame and long frame. The user can select the frame

structure by setting the SPI_I2SCFG.PCMFSYNC bits. The WS signal indicates frame synchronization information.

The WS signal for synchronizing long frames is 13 bits effective; the WS signal length for synchronizing short frames

is 1 bit.

The standard data receiving and sending processing mode is the same as I

2

S Philips standard.

CLK

WS

Send

Receive

SD

Left channel 32-bit

Right channel

LSB

16-bit data

16-bit data forced 0

MSB

MSB