17 12-BIT A/D CONVERTER (ADC12A)

17-6

Seiko Epson Corporation

S1C17M12/M13 TECHNICAL MANUAL

(Rev. 1.2)

17.5 Interrupts

The ADC12A has a function to generate the interrupts shown in Table 17.5.1.

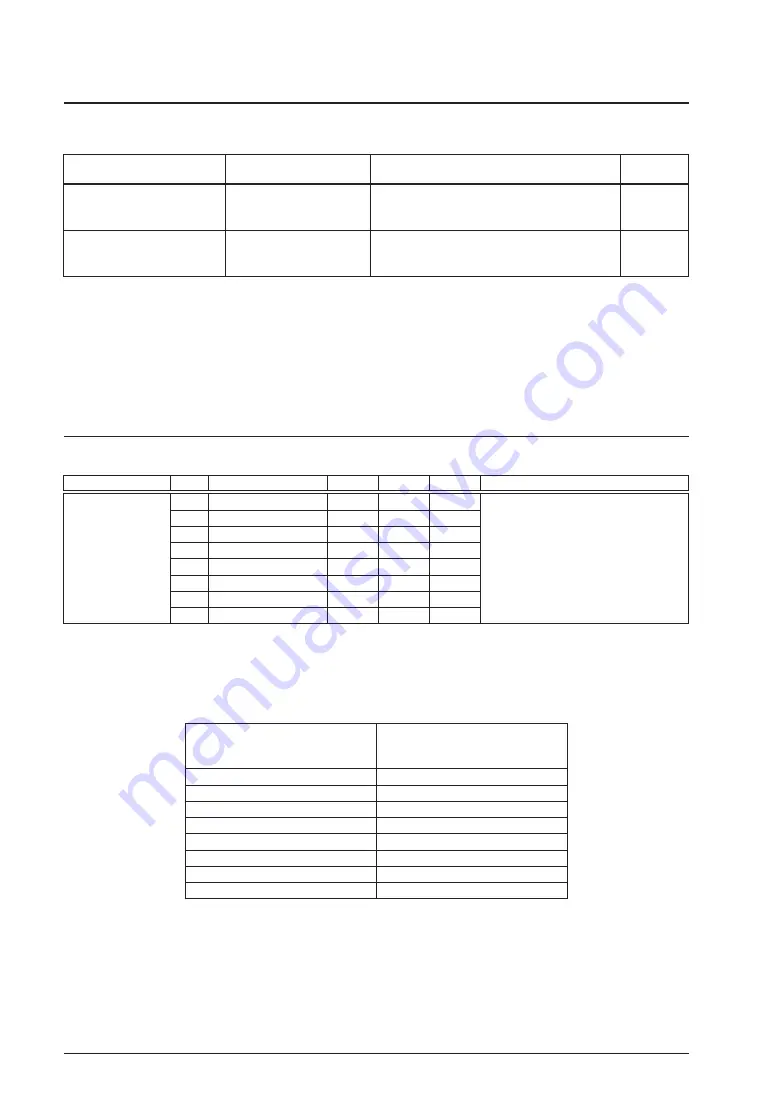

Table 17.5.1 ADC12A Interrupt Function

Interrupt

Interrupt flag

Set condition

Clear

condition

Analog input signal m A/D

conversion completion

ADC12_nINTF.ADmCIF

When an analog input signal m A/D conver-

sion result is loaded to the ADC12_nADmD

register

Writing 1

Analog input signal m A/D

conversion result overwrite

error

ADC12_nINTF.ADmOVIF When a new A/D conversion result is loaded

to the ADC12_nADmD register while the

ADC12_nINTF.ADmCIF bit = 1

Writing 1

Note that the A/D conversion continues even if an A/D conversion result overwrite error has occurred. A/D conver-

sion result overwrite errors are decided regardless of whether the ADC12_

n

AD

m

D register has been read or not.

The ADC12A provides interrupt enable bits corresponding to each interrupt flag. An interrupt request is sent to the

interrupt controller only when the interrupt flag, of which interrupt has been enabled by the interrupt enable bit, is

set. For more information on interrupt control, refer to the “Interrupt Controller” chapter.

17.6 Control Registers

ADC12A Ch.

n

Control Register

Register name

Bit

Bit name

Initial

Reset

R/W

Remarks

ADC12_nCTL

15 –

0

–

R

–

14–12 ADSTAT[2:0]

0x0

H0

R

11 –

0

–

R

10 BSYSTAT

0

H0

R

9–8 –

0x0

–

R

7–2 –

0x00

–

R

1

ADST

0

H0

R/W

0

MODEN

0

H0

R/W

Bit 15

Reserved

Bits 14–12 ADSTAT[2:0]

These bits indicate the analog input pin number

m

being A/D converted.

Table 17.6.1 Relationship Between Control Bit Value and Analog Input Pin

ADC12_nCTL.ADSTAT[2:0] bits

ADC12_nTRG.STAAIN[2:0] bits

ADC12_nTRG.ENDAIN[2:0] bits

Analog input pin

0x7

ADINn7

0x6

ADINn6

0x5

ADINn5

0x4

ADINn4

0x3

ADINn3

0x2

ADINn2

0x1

ADINn1

0x0

ADINn0

These bits indicate the last converted analog input pin number after A/D conversion is forcefully

terminated by writing 0 to the ADC12_

n

CTL.ADST bit or automatically terminated in one-time

conversion mode (ADC12_

n

TRG.CNVMD = 0). If A/D conversion is stopped after the maximum

analog input pin number (different in each model) has been completed, these bits indicate ADIN

n

0.

Bit 11

Reserved