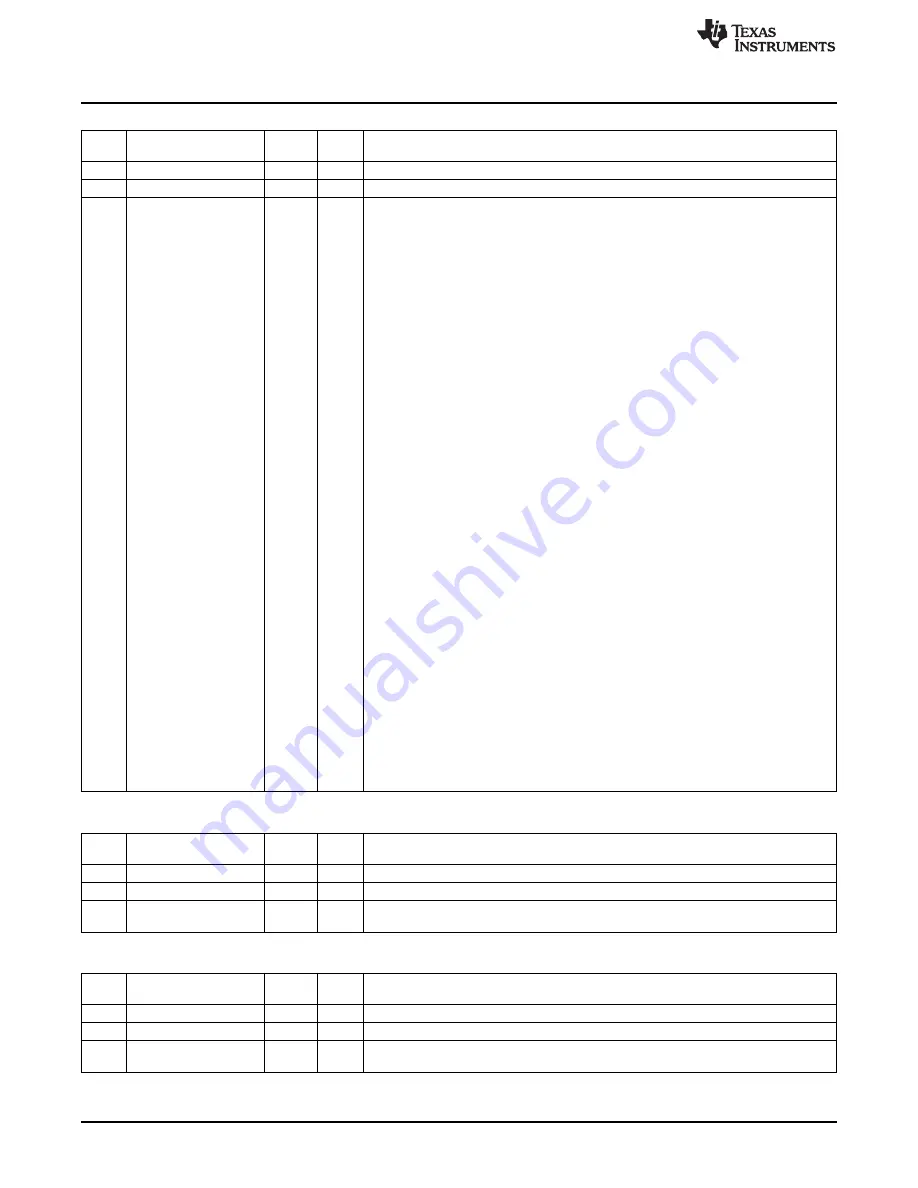

Registers

RFC_OBS_CTRL0 (0x61EB)

–

RF Observation Mux Control

Bit

Name

Reset

R/W

Description

No.

7

–

0

R0

Reserved. Read as 0

6

RFC_OBS_POL0

0

R/W

The signal chosen by RFC_OBS_MUX0 is XORed with this bit.

5:0

RFC_OBS_MUX0

00 0000 R/W

Controls which observable signal from RF Core is to be muxed out to rfc_obs_sigs[0].

00 0000: 0

–

Constant value

00 0001: 1

–

Constant value

00 1000: rfc_sniff_data

–

Data from packet sniffer. Sample data on rising edges of

sniff_clk.

00 1001: rfc_sniff_clk

–

250kHz clock for packet sniffer data.

00 1100: rssi_valid

–

Pin is high when the RSSI value has been updated at least once

since RX was started. Cleared when leaving RX.

00 1101: demod_cca

–

Clear channel assessment. See

FSMSTAT1

register for details

on how to configure the behavior of this signal.

00 1110: sampled_cca

–

A sampled version of the CCA bit from demodulator. The

value is updated whenever a SSAMPLECCA or STXONCCA strobe is issued.

00 1111: sfd_sync

–

Pin is high when a SFD has been received or transmitted.

Cleared when leaving RX/TX respectively. Not to be confused with the SFD exception.

01 0000: tx_active

–

Indicates that FFCTRL is in one of the TX states. Active-high.

Note: This signal might have glitches, because it has no output flip-flop and is based

on the current state register of the FFCTRL FSM.

01 0001: rx_active

–

Indicates that FFCTRL is in one of the RX states. Active-high.

Note: This signal might have glitches, because it has no output flip-flop and is based

on the current state register of the FFCTRL FSM.

01 0010: ffctrl_fifo

–

Pin is high when one or more bytes are in the RXFIFO. Low

during RXFIFO overflow.

01 0011: ffctrl_fifop

–

Pin is high when the number of bytes in the RXFIFO exceeds the

programmable threshold or at least one complete frame is in the RXFIFO. Also high

during RXFIFO overflow. Not to be confused with the FIFOP exception.

01 0100: packet_done

–

A complete frame has been received. I.e., the number of

bytes set by the frame-length field has been received.

01 0110: rfc_xor_rand_i_q

–

XOR between I and Q random outputs. Updated at 8

MHz.

01 0111: rfc_rand_q

–

Random data output from the Q channel of the receiver.

Updated at 8 MHz.

01 1000: rfc_rand_i

–

Random data output from the I channel of the receiver. Updated

at 8 MHz

01 1001: lock_status

–

1 when PLL is in lock, otherwise 0

10 1000: pa_pd

–

Power amplifier power-down signal

10 1010: lna_pd

–

LNA power-down signal

Others: Reserved

RFC_OBS_CTRL1 (0x61EC)

–

RF Observation Mux Control

Bit

Name

Reset

R/W

Description

No.

7

–

0

R0

Reserved. Read as 0

6

RFC_OBS_POL1

0

R/W

The signal chosen by

RFC_OBS_MUX1

is XORed with this bit.

5:0

RFC_OBS_MUX1

00 0000 R/W

Controls which observable signal from RF Core is to be muxed out to rfc_obs_sigs[1].

See description of

RFC_OBS_CTRL0

for details.

RFC_OBS_CTRL2 (0x61ED)

–

RF Observation Mux Control

Bit

Name

Reset

R/W

Description

No.

7

–

0

R0

Reserved. Read as 0

6

RFC_OBS_POL2

0

R/W

The signal chosen by

RFC_OBS_MUX2

is XORed with this bit.

5:0

RFC_OBS_MUX2

00 0000 R/W

Controls which observable signal from RF Core is to be muxed out to rfc_obs_sigs[2].

See description of

RFC_OBS_CTRL0

for details.

284

CC253x Radio

SWRU191C

–

April 2009

–

Revised January 2012

Copyright

©

2009

–

2012, Texas Instruments Incorporated