R8C/1A Group, R8C/1B Group

10. Clock Generation Circuit

Rev.1.30

Dec 08, 2006

Page 73 of 315

REJ09B0252-0130

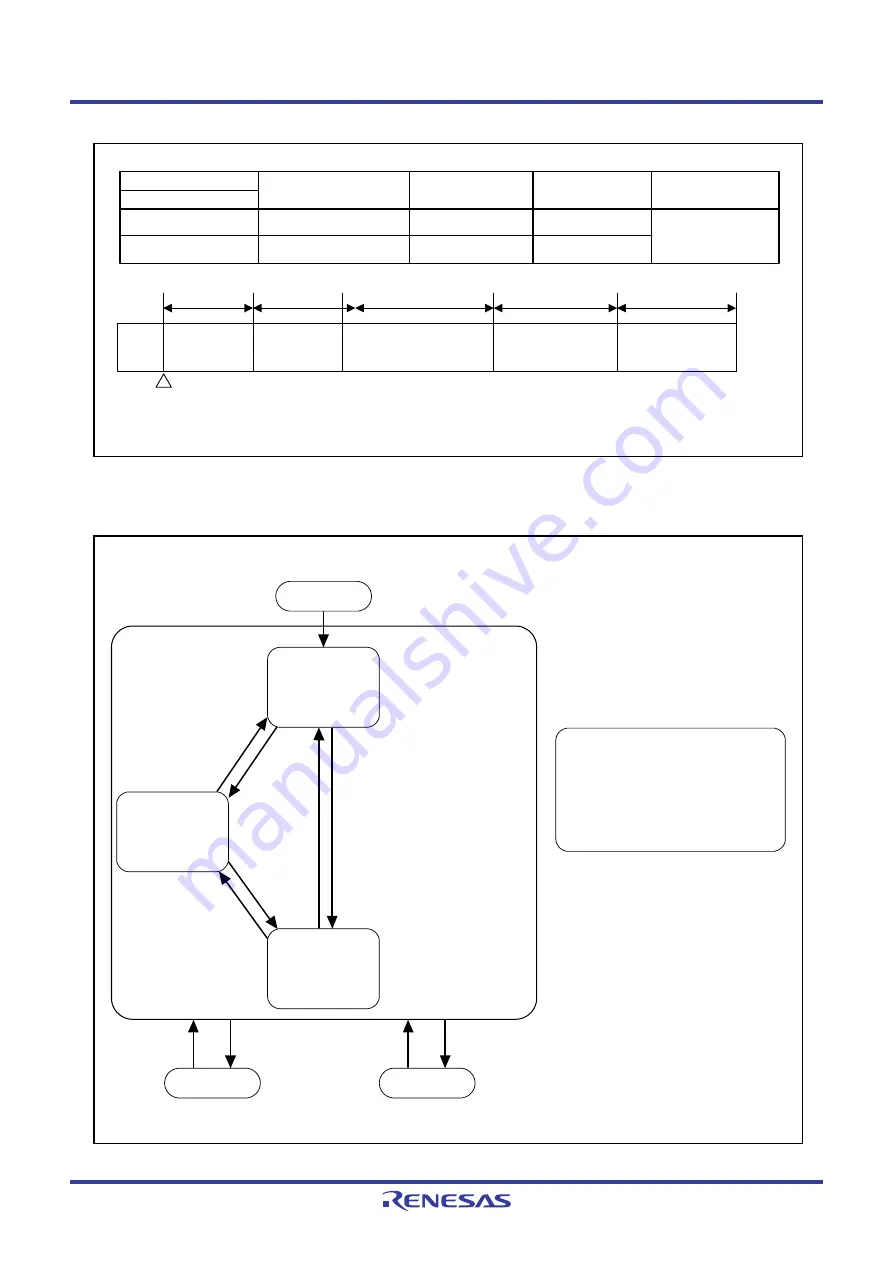

Figure 10.9

Time from Stop Mode to Interrupt Routine Execution

Figure 10.10 shows the State Transitions in Power Control.

Figure 10.10

State Transitions in Power Control

Time until Flash Memory

is Activated (T2)

T2

Period of CPU clock

×

6 cycles

Same as above

Period of CPU clock

×

20 cycles

Following total time is

the time from stop

mode until an interrupt

handling is executed.

FMSTP Bit

Period of system clock

×

12 30 µs (max.)

Period of system clock

×

12 cycles

Same as above

Time until CPU Clock

is Supplied (T3)

Time for Interrupt

Sequence (T4)

Remarks

Flash memory

activation sequence

CPU clock restart

sequence

Interrupt sequence

Oscillation time of

CPU clock source

used immediately

before stop mode

Stop

mode

T3

T4

Internal power

stability time

T1

T0

150 µs

(max.)

Interrupt

request

generated

0

(flash memory operates)

1

(flash memory stops)

FMR0 Register

There are six power control modes.

(1) High-speed mode

(2) Medium-speed mode

(3) High-speed on-chip oscillator mode

(4) Low-speed on-chip oscillator mode

(5) Wait mode

(6) Stop mode

CM05: Bit in CM0 register

CM10, CM13, CM14: Bit in CM1 register

OCD2: Bit in OCD register

HRA00, HRA01: Bit in HRA0 register

C

M

1

4

=

0

,

H

R

A

0

1

=

0

,

O

C

D

2

=

1

C

M

1

3

=

1

,

C

M

0

5

=

0

,

O

C

D

2

=

0

C

M

1

3

=

1

, C

M

0

5

=

0

,

O

C

D

2

=

0

High-speed mode,

medium-speed mode

High-speed on-chip

oscillator mode

OCD2 = 0

CM05 = 0

CM13 = 1

OCD2 = 1

HRA01 = 1

HRA00 = 1

Reset

Wait mode

Stop mode

Interrupt

CM10 = 1

(

all oscillators stop

)

Interrupt

WAIT

instruction

H

R

A

0

0

=

1

, H

R

A

0

1

=

1

,

O

C

D

2

=

1

HRA

0

0

=

1,

HRA

0

1

= 1

CM

1

4

=

1

,

HRA

01

=

0

OCD2 = 1

HRA01 = 0

CM14 = 0

Low-speed on-chip

oscillator mode