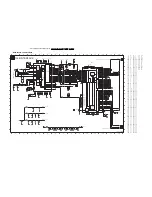

EN 128

DVDR880-890 /0X1

7.

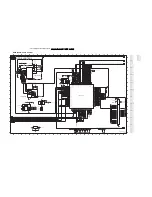

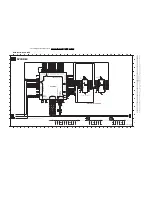

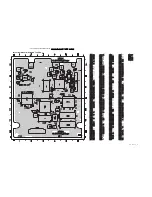

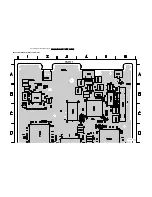

Circuit Diagrams and PWB Layouts

Digital Board: VSM, Buffer Memory and Bit Engine Interface

DVDR VERSATILE STREAM MANAGER

VSM

DQMH

SENSE AMPLIFIERS

COMMAND

DECODE

CTRL

LOGIC

MODE

REG

ADDRESS REGISTER

ROW

ADDR

MUX

LOGIC

CTRL

BANK

COLUMN

ADDR

COUNTER/

I/O GATING

DQM DATA LOGIC

READ DATA LATCH

WRITE DRIVERS

DATA INPUT REGISTER

DATA OUTPUT REGISTER

DQML

VDDQ

VDD

NC

VSSQ

VSS

LATCH

REFRESH

COUNTER

BANK0

ROW-

ADDR

LATCH &

DECODER

COLUMN

DEDCODER

BANK0

MEMORY

ARRAY

(4,096x256x16)

GND

PLL

t

Audio PLL

6

7

UART1

SYSTEM_CONTROL

SDRAM

13

14

15

A

B

C

D

E

F

G

H

A

B

C

D

E

F

G

H

11

12

1

2

3

4

5

JTAG_CHAIN3

SYSTEM DATA BUS

SYSTEM ADDRESS BUS

AUDIO ENCODER

8

9

10

11

12

13

14

15

1

2

3

4

5

6

7

8

9

10

TO BITENGINE

Encoding

MPEG2 VIDEO

DATA STREAM BUS

UART2

DIGITAL VIDEO(CCIR656)

BE_SERIAL

OPTION

OPTION

OPTION

OPTION

OPTION

OPTION

OPTION

OPTION

OPTION

GNDD

2154

10n

OPTION

OPTION

OPTION

OPTION

OPTION

OPTION

OPTION

OPTION

2153

100n

4109

4110

4107

4108

3113

4K7

4106

13

14

15

2

3

4

5

6

7

8

9

FMN

1101

1

10

11

12

22R

3117

I165

I174

I133

2107

100n

2122

100n

GNDD

2147

10p

2100

100n

I126

I143

47R

3128

12

46

52

16

WE_

47R

3129

DQ9

39 DQMH

15 DQML

36

40

18

RAS_

1

14

27

3

9

43

49

28

41

54

6

CS_

2 DQ0

4 DQ1

45 DQ10

47 DQ11

48 DQ12

50 DQ13

51 DQ14

53 DQ15

5 DQ2

7 DQ3

8 DQ4

10 DQ5

11 DQ6

13 DQ7

42 DQ8

44

A1

22

A10

35

A11

25

A2

26

A3

29

A4

30

A5

31

A6

32

A7

33

A8

34

A9

20

BA0

21

BA1

17

CAS_

37

CKE

38

CLK

19

2130

7101

MT48LC4M16A2TG-7E

23

A0

24

2u2

100MHZ

5103

3103

10K

I121

3132

1R

VSS_36

36

VSS_46

46

VSS_57

57

VSS_67

67

78

VSS_78

VSS_80

80

VSS_90

90

150

VSS_154

154

VSS_155

155

VSS_161

161

VSS_175

175

VSS_182

182

VSS_192

192

VSS_208

208

21

VSS_21

VSS_24

24

VSS_26

26

VE D9

119

VE DSn

127

VE DTACKn

128

VE VIP ERROR

142

VSS_10

10

VSS_100

100

116

VSS_116

VSS_130

130

VSS_132

132

VSS_135

135

VSS_150

VE D12

122

VE D13

123

VE D14

124

VE D15

125

111

VE D2

VE D3

112

VE D4

113

VE D5

114

VE D6

115

VE D7

117

VE D8

118

5

VDD_52

52

VDD_62

62

VDD_73

73

VDD_77

77

VDD_85

85

VDD_95

95

VE D0

109

110

VE D1

VE D10

120

VE D11

121

VDD_144

144

VDD_15

15

VDD_156

156

169

VDD_169

VDD_181

181

VDD_183

183

201

VDD_201

VDD_25

25

VDD_31

31

VDD_41

41

VDD_5

VBI IPD0

133

VBI IPD1

134

VBI IPD2

136

VBI IPD3

137

138

VBI IPD4

VBI IPD5

139

VBI IPD6

140

VBI IPD7

141

VDD_108

108

VDD_126

126

VDD_129

129

165

TRSTn

166

UART1 CTSn

148

UART1 RTSn

147

UART1 RX

145

UART1 TX

146

UART2 CTSn

153

UART2 RTSn

152

149

UART2 RX

UART2 TX

151

VBI ICLK

131

M_RASn

70

M_UDQM

75

M_Wen

76

RESETn

48

SYSCLK

47

TCK

162

163

TDI

164

TDO

TEST0

172

TEST1

173

TMS

M_D14

96

M_D15

98

M_D2

94

M_D3

92

89

M_D4

M_D5

87

M_D6

84

M_D7

82

M_D8

81

M_D9

83

M_LDQM

79

64

M_A9

66

M_CASn

74

M_CLKEN

71

M_CLKOUT

72

M_D0

99

M_D1

97

M_D10

86

88

M_D11

M_D12

91

M_D13

93

M_A10

63

M_A11

69

M_A12

65

M_A13

68

M_A2

55

M_A3

53

54

M_A4

M_A5

56

M_A6

59

M_A7

61

M_A8

12

HO_D5

11

HO_D6

9

HO_D7

8

7

HO_D8

HO_D9

6

HO_PROCCLK

18

HO_RWn

20

HO_WAIT

19

M_A0

60

M_A1

58

HO_D0

17

HO_D1

16

HO_D10

4

HO_D11

3

HO_D12

2

HO_D13

1

HO_D14

207

206

HO_D15

HO_D2

14

HO_D3

13

HO_D4

203

HO_A4

202

200

HO_A5

HO_A6

199

HO_A7

198

HO_A8

197

196

HO_A9

HO_BEN0

28

HO_BEN1

27

HO_CSHn

23

HO_CSLn

22

HO_A14

190

HO_A15

189

188

HO_A16

187

HO_A17

HO_A18

186

185

HO_A19

HO_A2

204

HO_A20

184

HO_A21

180

HO_A22

179

HO_A3

D V4

45

D WCLK

44

EXT INT0

171

EXT INT1

170

EXT INT2

168

EXT INT3

167

HO_A1

205

195

HO_A10

HO_A11

194

HO_A12

193

HO_A13

191

34

D PAR D2

39

40

D PAR D3

D PAR D4

42

D PAR D5

43

D PAR D6

35

37

D PAR D7

D PAR DVALID

38

D PAR REQ

30

D PAR STR

32

D PAR SYNC

29

BE BCLK

101

BE DATI

103

BE DATO

104

106

BE FLAG

BE SYNC

105

BE V4

107

BE WCLK

102

CPUINT0

50

CPUINT1

49

D PAR D0

33

D PAR D1

ACC ACLK DAI

160

ACC ACLK DEC

51

ACC ACLK OSC

158

ACC ACLK PLL

159

ACC FID

143

ACC PWM

157

176

AE BCLK

AE CS

174

AE DATA

178

AE WCLK

177

7100

SAA7333HL

I136

4105

100n

2112

I164

4u7

2127

GNDD

I134

I110

2129

68p

GND

2

3

1

6

VCC

5

4

7103

NC7SZ58

I124

I162

I176

47p

47R

3110

2141

3123

2K

3127

47R

GNDD

I101

I175

I106

I172

GNDD

GNDD

I119

100n

2132

I160

I120

I178

GNDD

I114

I118

2K2

3119

I117

GNDD

I182

10K

3102

I116

I171

I128

I145

I166

GNDD

GNDD

I115

I142

2118

100n

3K

3124

GNDD

5102

I107

I102

I156

10p

2148

2149

10p

3135

1R

I188

I163

100n

2101

I181

3136

1R

2152

10p

2139

100n

GNDD

I177

I113

22R

3118

I152

I112

3111

4K7

100n

2126

I184

GNDD

I104

I158

I130

100n

2123

I132

I170

GNDD

2111

100n

4100

R1

12

R2

15

RB

14

SIGI

16

VCC

9

VCOI

4

VCOO

10p

2134

74HCT9046AD

7102

6

C1A

7

C1B

3

COMPI

10

DEMO

1

8

5

INH

2

PC1O|PCPO

13

PC2O

11

I153

I109

220K

3126

I159

22R

3125

GNDD

I138

GNDD

3133

1R

3134

1R

3109

47R

11

12

13

14

15

2

3

4

5

6

7

8

9

GNDD

1100

FMN

1

10

I155

4K7

3114

2104

100n

GNDD

2114

100n

3120

15K

4101

2117

100n

1n

2128

I122

I105

I103

I125

2142

10p

10p

2143

2137

100n

47R

3106

2135

4u7

47R

3104

GNDD

GNDD

2125

100n

I179

3121

1R

3108

47R

GNDD

GNDD

10p

2140

GNDD

I108

100n

2102

GNDD

I127

12K

3122

2119

4u7

2105

100n

I140

10p

2150

I173

10p

I137

I141

2138

2120

100n

4K7

3112

I161

2116

100n

2136

GNDD

100n

2108

74HC1G04GW

7104

2

3

NC

1

5

4

47p

I157

47R

3105

100n

2121

I167

GNDD

I100

2144

10p

GNDD

GNDD

100n

2106

I180

I183

GNDD

4104

4102

5100

100MHZ

I186

I168

I131

I187

GNDD

GNDD

GNDD

3101

2K2

100n

2113

I129

100n

2146

I111

I123

5101

100MHZ

3116

10K

22u

2131

22p

2145

3137

4K7

4K7

3138

GNDD

3115

10K

I149

100n

2109

NTH5G16P

3130

10K

3100

2110

100n

10R

3107

I154

I169

I147

100n

2103

GNDD

4103

3131

1R

GNDD

2151

10p

100n

2115

100n

2124

BE_FAN

BE BCLK

BE WCLK

BE DATA RD

BE FLAG

BE SYNC

BE V4

VIP_INT

ACC ACLK PLL

VSM UART2 RX

VSM UART2 CTSn

+5V

+5V

BE IRQn

+3V3

VSM UART2 RTSn

AE_ACLK

JTAG3_TMS

JTAG3 TD VSM TO VIP

JTAG3_TCK

VSM M A(13 0)

VSM M D(15 0)

VSM UART1 RX

+3V3

BCLK CTL SERVICE

BE BCLK VSM

BE_LOADN

+5V

VCC5 4046

RESETn_BE

BE DATA WR

+5V

VSM UART2 TX

+5V

VSM UART1 RTSn

+5V

VSM UART1 TX

VCC3_VSM

JTAG3_TRSTn

AE DATAO

AE BCLK VSM

ACC_ACLK_OSC

VCC3_VSM

EMPRESS_IRQn

VCC3_VSM

VIP_FID_FF

D PAR SYNC

D PAR STR

D PAR REQ

D PAR DVALID

CPUINT1

CPUINT0

AE WCLK VSM

5508_odd_even

VIP ICLK

VSM UART1 CTSn

SYSCLK VSM 5508

RESETn

ACLK_EMP

VCC3_VSM

+5V

BE V4

BE FLAG

BE SYNC

BE DATA WR

BE DATA RD

BE WCLK

VIP ERROR

VE DTACKn

VE DSn

VCC3 VSM MEM

VSM_M_LDQM

{VSM M LDQM,VSM M UDQM,VSM M WEn,VSM M RASn,VSM M CASn,VSM M CLKEN,VSM M CLKOUT}

D PAR D(7 0)

VCC3 VSM

+3V3

+3V3

VSM M CASn

VSM M UDQM

VSM M RASn

VSM M WEn

VSM M CLKOUT

VSM M CLKEN

VERSATILE STREAM MANAGER (VSM), BUFFER MEMORY & BITENGINE INTERFACE

CL 16532145_022.eps

211101

1100

C1

1101

H1

2100

A4

2101

A5

2102

A5

2103

A5

2104

A5

2105

A5

2106

A5

2107

A5

2108

A5

2109

A5

2110

A5

2111

A5

2112

A5

2113

A5

2114

A5

2115

A6

2116

A6

2117

A6

2118

A6

2119

A4

2120

B15

2121

B15

2122

B14

2123

B14

2124

B13

2125

B13

2126

B12

2127

B12

2128

B3

2129

G13

2130

G15

2131

H15

2132

B1

2134

D1

2135

G13

2136

F1

2137

G4

2138

G1

2139

G13

2140

G2

2141

G2

2142

G2

2143

H1

2144

H1

2145

H1

2146

A4

2147

D1

2148

E1

2149

E1

2150

E1

2151

F1

2152

G1

3100

D11

3101

F10

3102

E3

3103

D11

3104

C2

3105

D2

3106

F2

3107

C3

3108

F3

3109

F3

3110

F3

3111

B3

3112

B3

3113

B3

3114

B2

3115

E3

3116

E3

3117

D11

3118

D11

3119

F10

3120

G15

3121

G12

3122

H12

3123

H12

3124

H12

3125

G14

3126

H12

3127

G3

3128

G2

3129

H2

3130

H12

3131

D2

3132

E2

3133

E2

3134

E2

3135

E2

3136

G1

3137

B2

3138

B2

4100

C15

4101

H4

4102

F6

4103

F7

4104

G6

4105

G7

5100

A4

5101

A12

5102

B1

5103

F13

7100

B4

7101

B14

7102

G13

7103

C1

7104

H4

Summary of Contents for DVDR880/001

Page 48: ...Mechanical Instructions EN 50 DVDR880 890 0X1 4 4 5 Dismantling Instructions Figure 4 14 ...

Page 166: ...Circuit IC Descriptions and List of Abbreviations EN 168 DVDR880 890 0X1 9 ...

Page 167: ...Circuit IC Descriptions and List of Abbreviations EN 169 DVDR880 890 0X1 9 ...

Page 174: ...Circuit IC Descriptions and List of Abbreviations EN 176 DVDR880 890 0X1 9 IC7411 ...

Page 182: ...Circuit IC Descriptions and List of Abbreviations EN 184 DVDR880 890 0X1 9 ...

Page 183: ...Circuit IC Descriptions and List of Abbreviations EN 185 DVDR880 890 0X1 9 ...

Page 184: ...Circuit IC Descriptions and List of Abbreviations EN 186 DVDR880 890 0X1 9 ...

Page 203: ...Circuit IC Descriptions and List of Abbreviations EN 205 DVDR880 890 0X1 9 ...