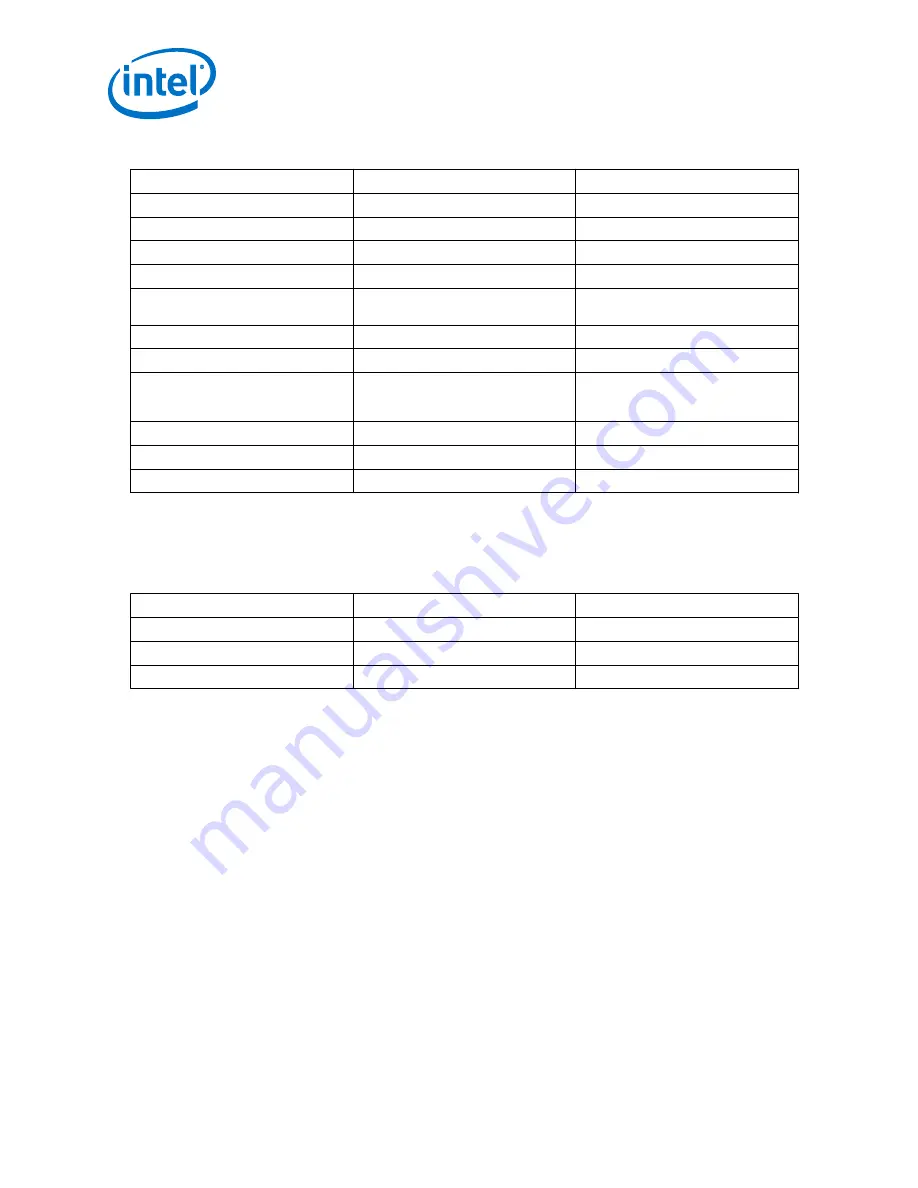

Table 1.

Summary of Per-channel Signals

Signal Name

Signal Width

Notes

Data

128

128 bit bidirectional DQ per channel

Column command/address

8

8-bit wide column address bits

Row command/address

6

6-bit wide row address bits

DBI

16

1 DBI per 8 DQs

DM_CB

16

1 DM per 8 DQs. You can use these

pins for DM or ECC, but not both.

PAR

4

1 parity bit per 32 DQs

DERR

4

1 data error bit per 32 DQs

Strobes

16

Separate strobes for read and write

strobes. One differential pair per 32

DQs for read and write.

Clock

2

Clocks address and command signals

CKE

1

Clock enable

AERR

1

Address error

The following table lists the HBM2 signals that are common to all Pseudo Channels in

each HBM2 interface. The HBM2 controller interfaces with the following signals; these

signals are not available at the AXI4 user interface.

Table 2.

Summary of Global HBM2 Signals

Signal Name

Signal Width

Notes

Reset

1

Reset input

TEMP

3

Temperature output from HBM2.

Cattrip

1

Catastrophic temperature sensor.

The Intel Stratix 10 MX HBM2 IP supports only the Pseudo Channel mode of the HBM2

specification. Pseudo Channel mode includes the following features:

•

Pseudo Channel mode divides a single HBM2 channel into two individual

subchannels of 64 bit I/O.

•

Both Pseudo Channels share the channel’s row and column command bus, CK, and

CKE inputs, but decode and execute commands individually.

•

Pseudo Channel mode requires a burst length of 4.

•

Address BA4 directs commands to either Pseudo Channel 0 (BA4 = 0) or Pseudo

Channel 1 (BA4 = 1). The HBM2 controller handles the addressing requirements of

the Pseudo Channels.

•

Power-down and self-refresh are common to both Pseudo Channels, due to a

shared CKE pin. Both Pseudo Channels also share the channel’s mode registers.

Each Intel Stratix 10 MX HBM2 interface supports a maximum of eight HBM2 channels.

Each HBM2 channel has two AXI4 interfaces, one per Pseudo Channel. The following

figure shows the flow of data from user logic to the HBM2 DRAM through the UIBSS,

while selecting HBM2 channels 0 and 7.

2 Intel Stratix 10 MX HBM2 Architecture

UG-20031 | December 2017

Intel

®

Stratix

®

10 MX HBM2 IP User Guide

8