GV-395 Virtex-II DSP Hardware Accelerator Manual

GV & Associates, Inc.

07/10/04

26

11.3

DPX USB Interface

The Cypress CY7C68001 USB Controller (U21) is connected to both Virtex-II FPGAs (U14). An software and

firmware interface design is available. The link to the design on our web site is

(

http://www.gvassociates.com/software.asp?prod=12

). Additional documentation is also available.

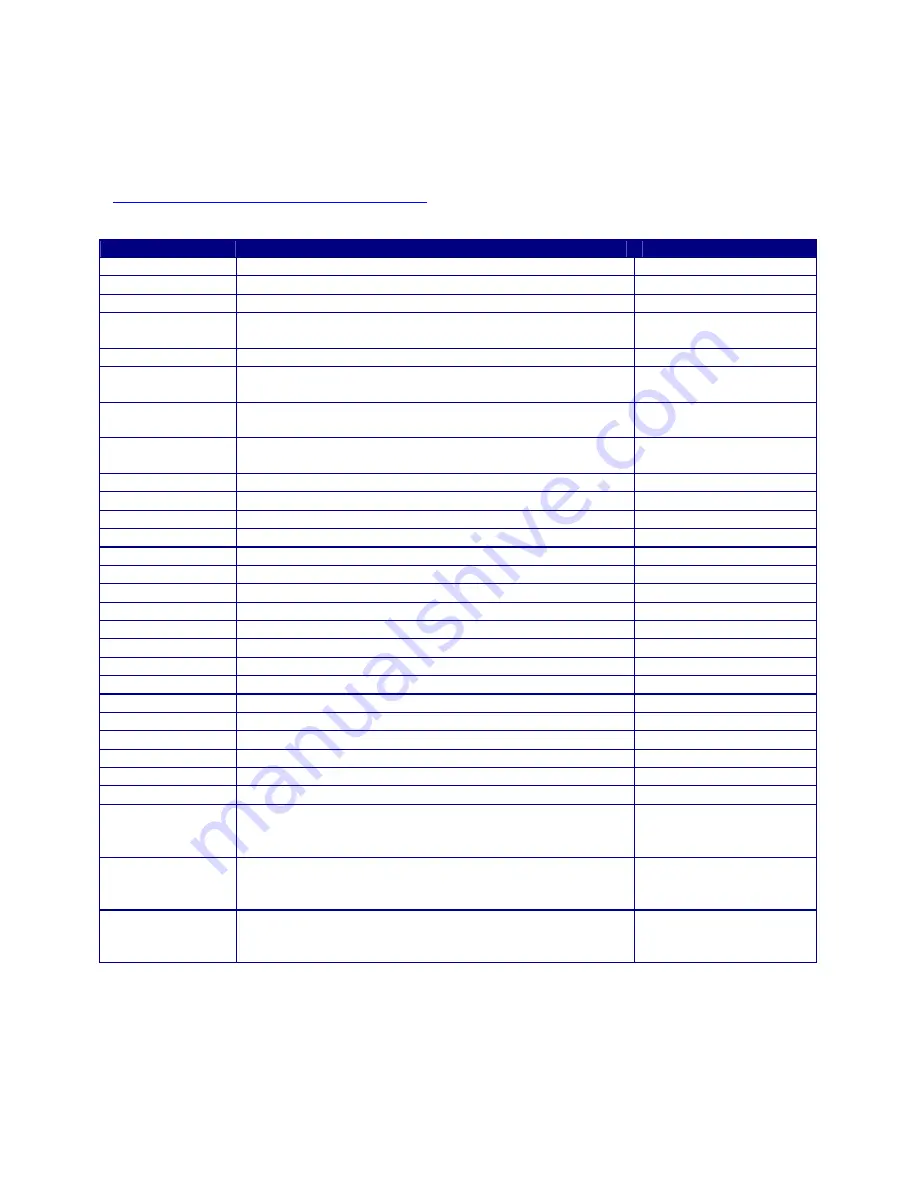

Signal Name

Signal Description

DP FPGA (U14) Pin No.

USB1_SLRD

read strobe for the slave FIFOs connected to FDI[15..0]

AK34

USB1_SLWR

write strobe for the slave FIFOs connected to FDI[15..0]

AF27

USB1_SLOE

output enable for the slave FIFOs connected to FD[15..0]

AG28

USB1_READY

ready that gates external command reads andwrites. Active

High.

USB1_INT

external interrupt signal. Active Low.

USB1_FIFOADR2 address bus select for the slave FIFOs connected to FD[15..0]

AF30

USB1_FIFOADR1 address bus select for the slave FIFOs connected to FD[15..0]

AG30

USB1_FIFOADR0 address bus select for the slave FIFOs connected to FD[15..0]

AE29

USB1_PKTEND

packet end signal for the slave FIFOs connected to FD[15..0]

AF29

USB1_CS# master

chip

select (active low)

AE27

USB1_FD15

Bidirectional FIFO/Command Data Bit 15

AG31

USB1_FD14

Bidirectional FIFO/Command Data Bit 14

AF31

USB1_FD13

Bidirectional FIFO/Command Data Bit 13

AG32

USB1_FD12

Bidirectional FIFO/Command Data Bit 12

AF32

USB1_FD11

Bidirectional FIFO/Command Data Bit 11

AB25

USB1_FD10

Bidirectional FIFO/Command Data Bit 10

AC25

USB1_FD9

Bidirectional FIFO/Command Data Bit 9

AH33

USB1_FD8

Bidirectional FIFO/Command Data Bit 8

AJ33

USB1_FD7

Bidirectional FIFO/Command Data Bit 7

AD32

USB1_FD6

Bidirectional FIFO/Command Data Bit 6

AE31

USB1_FD5

Bidirectional FIFO/Command Data Bit 5

AC27

USB1_FD4

Bidirectional FIFO/Command Data Bit 4

AD27

USB1_FD3

Bidirectional FIFO/Command Data Bit 3

AH34

USB1_FD2

Bidirectional FIFO/Command Data Bit 2

AJ34

USB1_FD1

Bidirectional FIFO/Command Data Bit 1

AD30

USB1_FD0

Bidirectional FIFO/Command Data Bit 0

AE30

USB1_FLAGA

a programmable slave-FIFO output status flag signal.

Defaults to PRGFLAG for the FIFO selected by the

FIFOADR[1:0] pins

AE26

USB1_FLAGB

a programmable slave-FIFO output status flag signal.

Defaults to FULL for the FIFO selected by the FIFOADR[2:0]

pins.

AD26

USB1_FLAGC

a programmable slave-FIFO output status flag signal.

Defaults to EMPTY for the FIFO selected by the

FIFOADR[2:0] pins.

AE28

11.3.1

USB Interface for DPX FPGA Interconnection Table