GV-395 Virtex-II DSP Hardware Accelerator Manual

GV & Associates, Inc.

07/10/04

36

13.3

GVA-DA6645 100 MSPS 14 Bit A/D

The analog input is injected via a 50-ohm SMA connector (P1). The analog input voltage should not exceed 2 Vp-p.

The input Analog – Digital Converter (DA6645) is protected against accidental application of an over-voltage input

by a protection diodes. The digital data generated by the Analog to Digital Converters is buffered by

74ALVCH16374 (a 16 bit D register). This buffer incurs a one-clock delay between the A/D and the FPGA. This

was necessary to insure proper data setup time for the FPGA. The analog signals are each sampled by a 100 MSPS

analog to digital converter (DA6645). The input sample clock (DA_CLK) can be set to a maximum frequency of

100 MHz via the Analog Control FPGA (U14). The sample clock may be generated either the 100 MHz system

clock or from the External Clock Input (P6). The LVTTL clock signal is coupled with a differential receiver

(MC10EL16). The output of this differential receiver drive the ENCODE and ENCODE- inputs of the converter and

provides the sub-nanosecond rise times for optimum performance.

13.3.1

AC Coupled Analog Input Path

The analog input is AC coupled into two Mini-Circuits T1:1 transformer, which has a high pass corner at 50 KHz.

These transformers are used to generate a differential input to the DA6645. To reduce the second harmonic

distortion two T1-1T transformers are connected in series. A 3 dB to 4 dB improvement can be realized.

DAditionally, an external anti-aliasing filter may be needed to limit the input bandwidth of the A/D.

13.3.2

DC Coupled Analog Input Path

A differential output op amp (DA8138) is used to drive the DA6645 in the dc-coupled configuration. The DA8138

was specifically designed for DAC driver applications and has superior SNR performance in analog frequencies

from 0 thru 30 MHz.

13.3.3

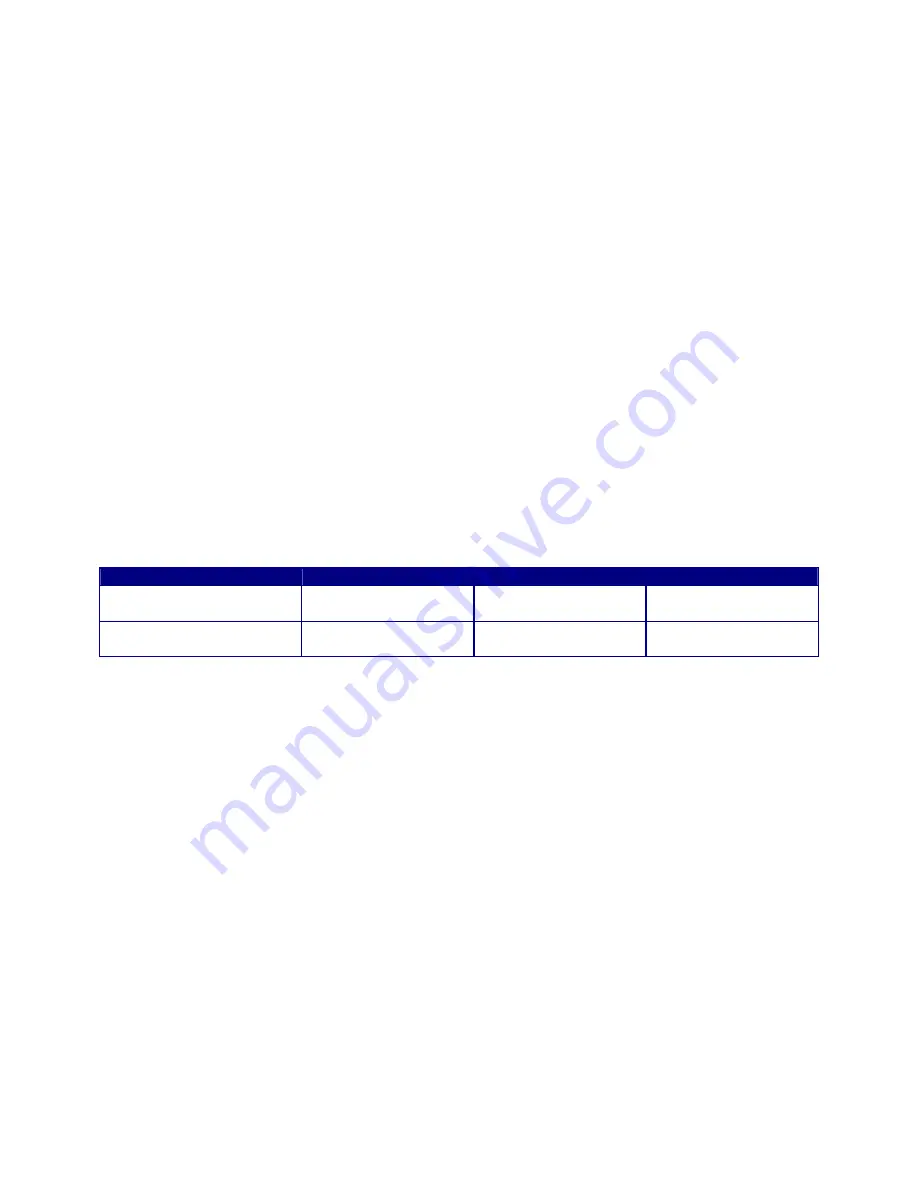

GVA-DA6645 Analog Input Configuration

Input Configuration

JP1

JP2

JP3

AC-Coupled Analog Input

Jumper on pin 1 and

pin 2

Jumper on pin 1 and

pin 2

Jumper on pin 1 and

pin 2

DC-Coupled Analog Input

Jumper on pin 2 and

pin 3

Jumper on pin 2 and

pin 3

Jumper on pin 2 and

pin 3

13.3.3.1

GVA-AD6645 Analog Input Jumper Configuration Table

* Pin 1 is the closest pin to GV & Associates logo on the PCB.