SIC63616-(Rev. 1.0) NO. P180

3240-0412

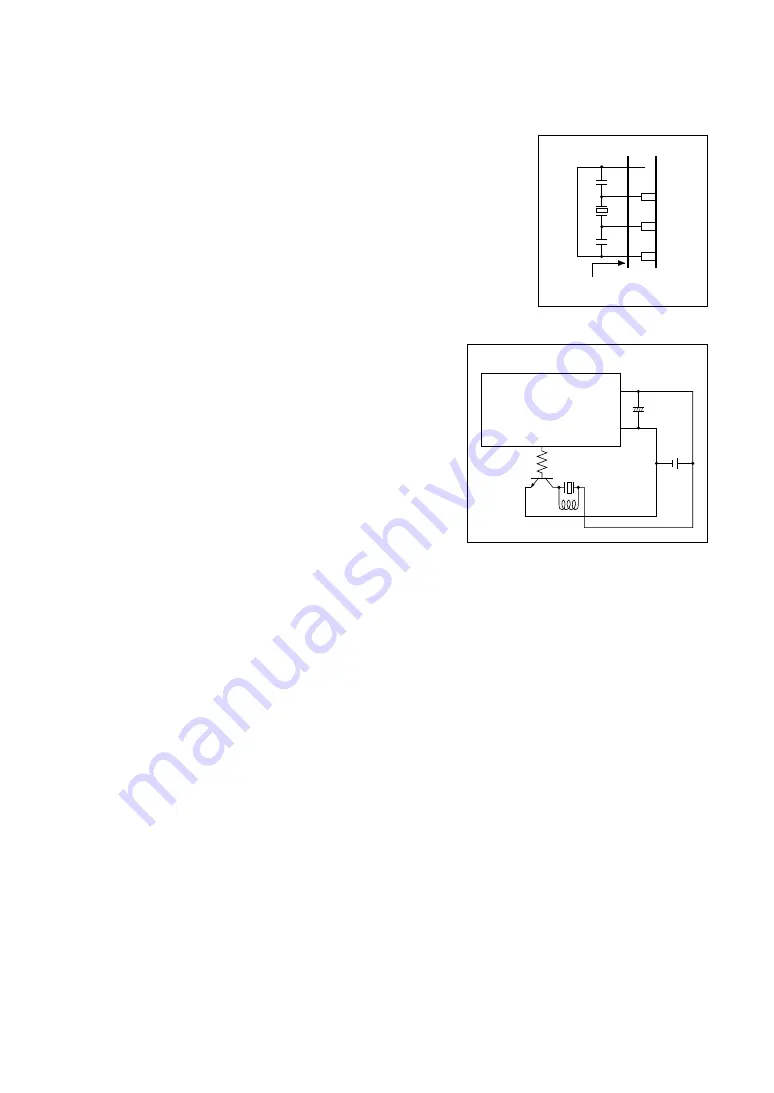

<Arrangement of Signal Lines>

●

In order to prevent generation of electromagnetic induction noise caused by mutual inductance, do not

arrange a large current signal line near the circuits that are sensitive to noise such as the oscillation unit

and analog input unit.

●

When a signal line is parallel with a high-speed line in long distance

or intersects a high-speed line, noise may generated by mutual inter-

ference between the signals and it may cause a malfunction.

Do not arrange a high-speed signal line especially near circuits that

are sensitive to noise such as the oscillation unit and analog input

unit.

OSC4

OSC3

V

SS

Large current signal line

High-speed signal line

Prohibited pattern example

<Output Terminals>

●

When an output terminal is used to drive an external

component that consumes a large amount of current, the

operation of the external component affects the built-in

power supply circuit of this IC and the output voltage may

vary. When driving a bipolar transistor by a periodic signal

such as the BZ or timer output in particular, it may cause

variations in the voltage output from the LCD system volt-

age circuit that affects the contrast of the LCD display. To

prevent this, separate the traces on the printed circuit board.

Put one between the power supply and the IC's V

DD

and

V

SS

terminals, and another between the power supply and

the external component that consumes the large amount of

current. Furthermore, use an external component with as

low a current consumption as possible.

V

DD

V

SS

Piezo

BZ

C

P

Example: Buzzer output circuit

+

<Precautions for Visible Radiation (when bare chip is mounted)>

●

Visible radiation causes semiconductor devices to change electrical characteristics. It may cause the IC

to malfunction. When developing products, consider the following precautions to prevent malfunctions

caused by visible radiation.

(1) Design the product and bond the IC on the board so that it is shielded from visible radiation in ac-

tual use.

(2) The inspection process of the product needs an environment that shields the IC from visible radia-

tion.

(3) Shield not only the face of the IC but the back and side as well.

(4) After the shielded package has been opened, the IC chip should be bonded on the board within one

week. If the IC chip must be stored after the package has been opened, be sure to shield the IC from

visible radiation.

(5) If there is a possibility that heat stress exceeding the reflow soldering condition is applied to the IC

in the bonding process, perform enough evaluation of data stored in the nonvolatile memory before

the product is shipped.