H O S T I N T E R F A C E

Data Device Corporation

DS-BU-67301B-G

1/14

28

multiplexed mode, the host’s address is presented over CPU_DATA(15:0), prior to

the data phase of the transfer.

For applications demanding the fastest data throughput performance, use of either

the Synchronous CPU interface or the

Total-AceXtreme’s

PCI interface is

recommended. This is because both of these interfaces support burst transfers.

Bursting for the Synchronous CPU interface can be for either 32-bit or 16-bit words,

at rates up to 80 Mwords/s.

6.2.1 Static Configuration Signals

The

Total-AceXtreme®

includes four static input signals for establishing the

configuration for the host interface: PCI_nCPU, DATA32_n16,

CPU_ASYNC_nSYNC, and ADMULTI. The operation of these signals is shown in

Table 3. Note that DATA32_n16, CPU_ASYNC_nSYNC, and ADMULTI have no

affect on the operation of the

Total-AceXtreme’s

PCI interface.

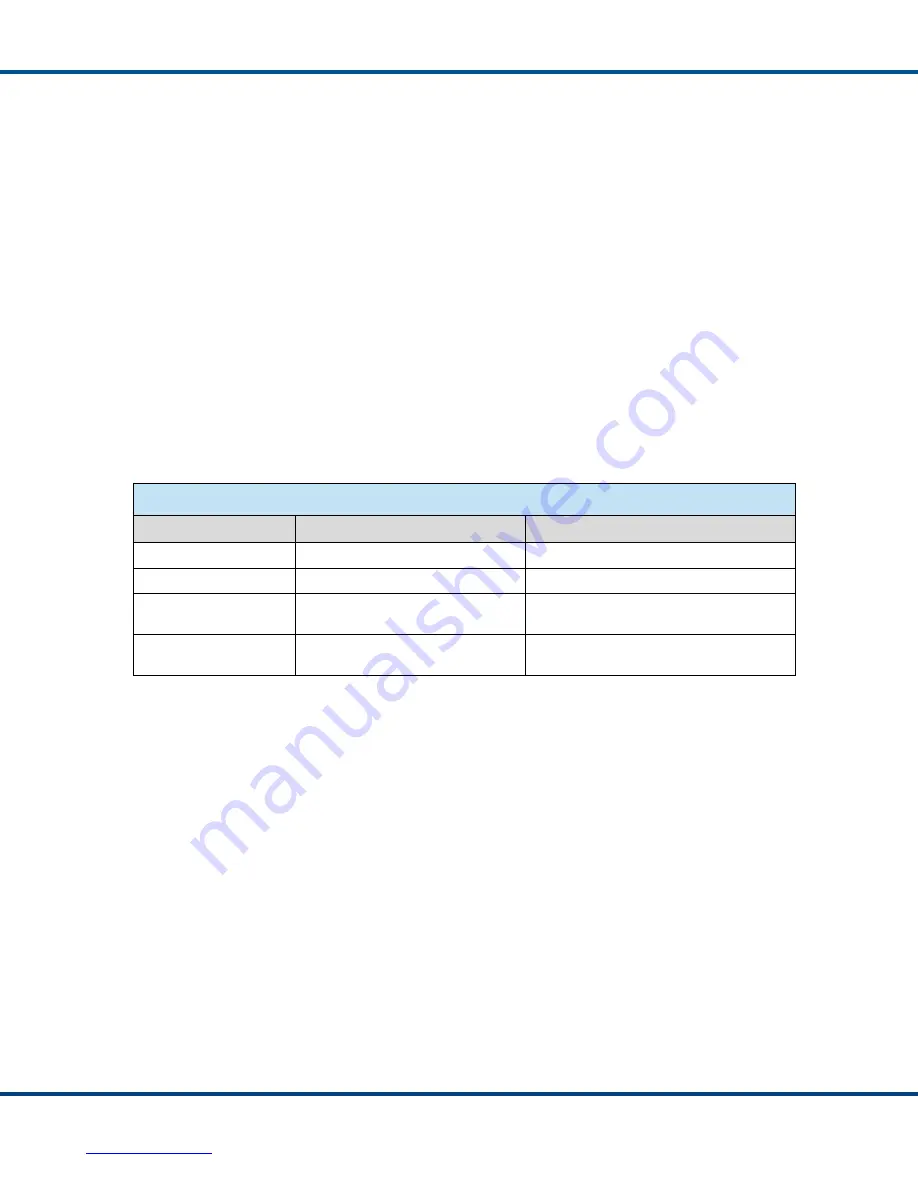

Table 3. Total-AceXtreme® Host

Interface Configuration Options

Input Signal Name

Operation if Logic ‘1’

Operation if Logic ‘0’

PCI_nCPU

32-bit Target/Initiator PCI Interface

Parallel CPU Interface

DATA32_n16

32-bit Parallel CPU Interface

16 Bit Parallel CPU Interface

CPU_ASYNC_nSYNC

Asynchronous Parallel CPU

Interface

Synchronous Parallel CPU Interface

ADMULTI

Multiplex Address/Data Mode for

Parallel CPU Interface

Separate Address and Data Buses for

Parallel CPU Interface

6.2.2 Parallel CPU Interface Signals

The following input and outputs signals are common to all or most of the parallel CPU

interface modes:

6.2.2.1 I/O Signals

•

CPU_DATA(31:0):

Bi-directional 32-bit host bit data bus. In 16-bit mode, only CPU_DATA(15:0) is

used, while CPU_DATA(31:16) is not used. The operation of CPU_DATA(31:0)

varies as a function of which host CPU interface configuration is used. For the

multiplexed address/data modes, the host presents its memory or register

address to the

Total-AceXtreme

on CPU_DATA(15:0) and must assert

ADDR_LAT high during this time.