30

4317I–AVR–01/08

AT90PWM2/3/2B/3B

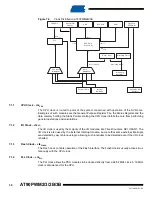

Figure 7-2.

Clock Distribution AT90PWM2B/3B

7.1.1

CPU Clock – clk

CPU

The CPU clock is routed to parts of the system concerned with operation of the AVR core.

Examples of such modules are the General Purpose Register File, the Status Register and the

data memory holding the Stack Pointer. Halting the CPU clock inhibits the core from performing

general operations and calculations.

7.1.2

I/O Clock – clk

I/O

The I/O clock is used by the majority of the I/O modules, like Timer/Counters, SPI, USART. The

I/O clock is also used by the External Interrupt module, but note that some external interrupts

are detected by asynchronous logic, allowing such interrupts to be detected even if the I/O clock

is halted.

7.1.3

Flash Clock – clk

FLASH

The Flash clock controls operation of the Flash interface. The Flash clock is usually active simul-

taneously with the CPU clock.

7.1.4

PLL Clock – clk

PLL

The PLL clock allows the PSC modules to be clocked directly from a 64/32 MHz clock. A 16 MHz

clock is also derived for the CPU.

General I/O

Modules

ADC

CPU Core

RAM

clk

I/O

AVR Clock

Control Unit

clk

CPU

Flash and

EEPROM

clk

FLASH

clk

ADC

Source Clock

Watchdog Timer

Watchdog

Oscillator

Reset Logic

Clock

Multiplexer

Watchdog Clock

Calibrated RC

Oscillator

(Crystal

Oscillator)

External Clock

PSC0/1/2

PLL

CLK

PLL

Multiplexer

PLL Input