Page 60

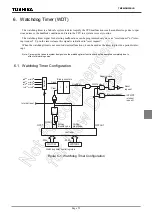

6. Watchdog Timer (WDT)

6.2 Watchdog Timer Control

TMP86PM29BUG

6.2

Watchdog Timer Control

The watchdog timer is controlled by the watchdog timer control registers (WDTCR1 and WDTCR2). The watch-

dog timer is automatically enabled after the reset release.

6.2.1

Malfunction Detection Methods Using the Watchdog Timer

The CPU malfunction is detected, as shown below.

1. Set the detection time, select the output, and clear the binary counter.

2. Clear the binary counter repeatedly within the specified detection time.

If the CPU malfunctions such as endless loops or the deadlock conditions occur for some reason, the watch-

dog timer output is activated by the binary-counter overflow unless the binary counters are cleared. When

WDTCR1<WDTOUT> is set to “1” at this time, the reset request is generated and the

RESET

pin outputs a

low-level signal, then internal hardware is initialized. When WDTCR1<WDTOUT> is set to “0”, a watchdog

timer interrupt (INTWDT) is generated.

The watchdog timer temporarily stops counting in the STOP mode including the warm-up or IDLE/SLEEP

mode, and automatically restarts (continues counting) when the STOP/IDLE/SLEEP mode is inactivated.

Note:The watchdog timer consists of an internal divider and a two-stage binary counter. When the clear code 4EH

is written, only the binary counter is cleared, but not the internal divider. The minimum binary-counter overflow

time, that depends on the timing at which the clear code (4EH) is written to the WDTCR2 register, may be 3/

4 of the time set in WDTCR1<WDTT>. Therefore, write the clear code using a cycle shorter than 3/4 of the

time set to WDTCR1<WDTT>.

Example :Setting the watchdog timer detection time to 2

21

/fc [s], and resetting the CPU malfunction detection

LD

(WDTCR2), 4EH

: Clears the binary counters.

LD

(WDTCR1), 00001101B

: WDTT

←

10, WDTOUT

←

1

LD

(WDTCR2), 4EH

: Clears the binary counters (always clears immediately before and

after changing WDTT).

Within 3/4 of WDT

detection time

:

:

LD

(WDTCR2), 4EH

: Clears the binary counters.

Within 3/4 of WDT

detection time

:

:

LD

(WDTCR2), 4EH

: Clears the binary counters.

Содержание TLCS-870/C Series

Страница 1: ...8 Bit Microcontroller TLCS 870 C Series TMP86PM29BUG ...

Страница 6: ...TMP86PM29BUG ...

Страница 7: ...Revision History Date Revision 2007 10 11 1 First Release 2008 8 29 2 Contents Revised ...

Страница 9: ......

Страница 15: ...vi ...

Страница 19: ...Page 4 1 3 Block Diagram TMP86PM29BUG 1 3 Block Diagram Figure 1 2 Block Diagram ...

Страница 23: ...Page 8 1 4 Pin Names and Functions TMP86PM29BUG ...

Страница 48: ...Page 33 TMP86PM29BUG ...

Страница 49: ...Page 34 2 Operational Description 2 3 Reset Circuit TMP86PM29BUG ...

Страница 61: ...Page 46 3 Interrupt Control Circuit 3 8 External Interrupts TMP86PM29BUG ...

Страница 81: ...Page 66 6 Watchdog Timer WDT 6 3 Address Trap TMP86PM29BUG ...

Страница 135: ...Page 120 10 8 Bit TimerCounter TC5 TC6 10 1 Configuration TMP86PM29BUG ...

Страница 145: ...Page 130 11 Asynchronous Serial interface UART 11 9 Status Flag TMP86PM29BUG ...

Страница 165: ...Page 150 13 10 bit AD Converter ADC 13 6 Precautions about AD Converter TMP86PM29BUG ...

Страница 183: ...Page 168 15 LCD Driver 15 4 Control Method of LCD Driver TMP86PM29BUG ...

Страница 201: ...Page 186 18 Electrical Characteristics 18 9 Handling Precaution TMP86PM29BUG ...

Страница 203: ...Page 188 19 Package Dimensions TMP86PM29BUG ...

Страница 205: ......