Page 178

18. Electrical Characteristics

18.2 Recommended Operating Condition

TMP86PM29BUG

18.2 Recommended Operating Condition

The recommended operating conditions for a device are operating conditions under which it can be guaranteed that

the device will operate as specified. If the device is used under operating conditions other than the recommended

operating conditions (supply voltage, operating temperature range, specified AC/DC values etc.), malfunction may

occur. Thus, when designing products which include this device, ensure that the recommended operating conditions

for the device are always adhered to.

(V

SS

= 0 V, Topr =

−

40 to 85

°

C)

Parameter

Symbol

Pins

Condition

Min

Max

Unit

Supply voltage

V

DD

fc = 16 MHz

NORMAL1, 2 mode

4.5

5.5

V

IDLE0, 1, 2 mode

fc = 8 MHz

NORMAL1, 2 mode

2.7

IDLE0, 1, 2 mode

fc = 4.2

MHz

NORMAL1, 2 mode

1.8

IDLE0, 1, 2 mode

fs = 32.768

kHz

SLOW1, 2 mode

SLEEP0, 1, 2 mode

STOP mode

Input high level

V

IH1

Except hysteresis input

V

DD

≥

4.5 V

V

DD

×

0.70

V

DD

V

IH2

Hysteresis input

V

DD

×

0.75

V

IH3

V

DD

< 4.5 V

V

DD

×

0.90

Input low level

V

IL1

Except hysteresis input

V

DD

≥

4.5 V

0

V

DD

×

0.30

V

IL2

Hysteresis input

V

DD

×

0.25

V

IL3

V

DD

< 4.5 V

V

DD

×

0.10

Clock frequency

fc

XIN, XOUT

V

DD

= 1.8 V to 5.5 V

1.0

4.2

MHz

V

DD

= 2.7 V to 5.5 V

8.0

V

DD

= 4.5 V to 5.5 V

16.0

fs

XTIN, XTOUT

30.0

34.0

kHz

Содержание TLCS-870/C Series

Страница 1: ...8 Bit Microcontroller TLCS 870 C Series TMP86PM29BUG ...

Страница 6: ...TMP86PM29BUG ...

Страница 7: ...Revision History Date Revision 2007 10 11 1 First Release 2008 8 29 2 Contents Revised ...

Страница 9: ......

Страница 15: ...vi ...

Страница 19: ...Page 4 1 3 Block Diagram TMP86PM29BUG 1 3 Block Diagram Figure 1 2 Block Diagram ...

Страница 23: ...Page 8 1 4 Pin Names and Functions TMP86PM29BUG ...

Страница 48: ...Page 33 TMP86PM29BUG ...

Страница 49: ...Page 34 2 Operational Description 2 3 Reset Circuit TMP86PM29BUG ...

Страница 61: ...Page 46 3 Interrupt Control Circuit 3 8 External Interrupts TMP86PM29BUG ...

Страница 81: ...Page 66 6 Watchdog Timer WDT 6 3 Address Trap TMP86PM29BUG ...

Страница 135: ...Page 120 10 8 Bit TimerCounter TC5 TC6 10 1 Configuration TMP86PM29BUG ...

Страница 145: ...Page 130 11 Asynchronous Serial interface UART 11 9 Status Flag TMP86PM29BUG ...

Страница 165: ...Page 150 13 10 bit AD Converter ADC 13 6 Precautions about AD Converter TMP86PM29BUG ...

Страница 183: ...Page 168 15 LCD Driver 15 4 Control Method of LCD Driver TMP86PM29BUG ...

Страница 201: ...Page 186 18 Electrical Characteristics 18 9 Handling Precaution TMP86PM29BUG ...

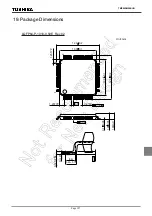

Страница 203: ...Page 188 19 Package Dimensions TMP86PM29BUG ...

Страница 205: ......