Application Note P4097

© TeraTron GmbH

Page 13 of 21

V1.1, 07.06.01

resonance frequency and compare it with given limits. These limits are usually much more narrow

than the PLL locking range is.

4. Antenna Design

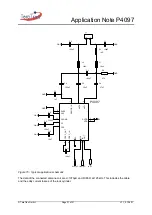

The reader/exciter antenna is a series resonance circuit which consists of an inductor, a capacitor and

a resistor. The characterizing variables of this circuit are the resonance frequency f

res

and the quality

factor Q.

The resonance frequency is calculated with:

C

L

f

res

⋅

⋅

Π

⋅

=

2

1

The quality factor is given with:

R

L

f

Q

res

⋅

⋅

Π

⋅

=

2

The resistor R should be measured at the resonance frequency for the case that magnetic or electric

conductive material is located in the vicinity of the coil. R is then the sum of resistive, eddy current and

hysteresis losses. Furthermore the resistive losses are the sum of the copper resistance of the

antenna, possibly the parasitic resistance of EMC coils and the resistance of the antenna driver, given

in the datasheet as R

AD

.

For measuring the value of Q the voltage over the inductor or the capacitor can be used. The formula

is given as:

DD

L

V

Q

V

⋅

Π

⋅

=

4

ˆ

Not only the voltage over C and L are linear dependant from Q, also the current through the series

resonance circuit depends from Q.

R

V

I

DD

Ant

⋅

Π

=

4

ˆ

This current should be chosen with regard to the datasheet, there are three limits to pay attention to,

one for continuous operation, the other for pulsed operation and the third is the resulting power

dissipation affecting the chip temperature. Violating these limits will affect the performance or the

lifetime of the chip.

To get a feeling for the antenna parameters the current as function of Q for different quality factors is

drawn in the figure below.