Remote Control

CTS60

1094.0006.60

8.20

E-3

8.8.3

Description of the Status Registers

8.8.3.1

Status Byte (STB) and Service Request Enable Register (SRE)

The STB is already defined in IEEE 488.2. It provides a rough overview of the instrument status by

collecting the pieces of information of the lower registers. It can thus be compared with the CONDition

part of an SCPI register and assumes the highest level within the SCPI hierarchy. A special feature is

that bit 6 acts as the sum bit of the remaining bits of the status byte.

The STATUS BYTE is read out using the command "*STB?".

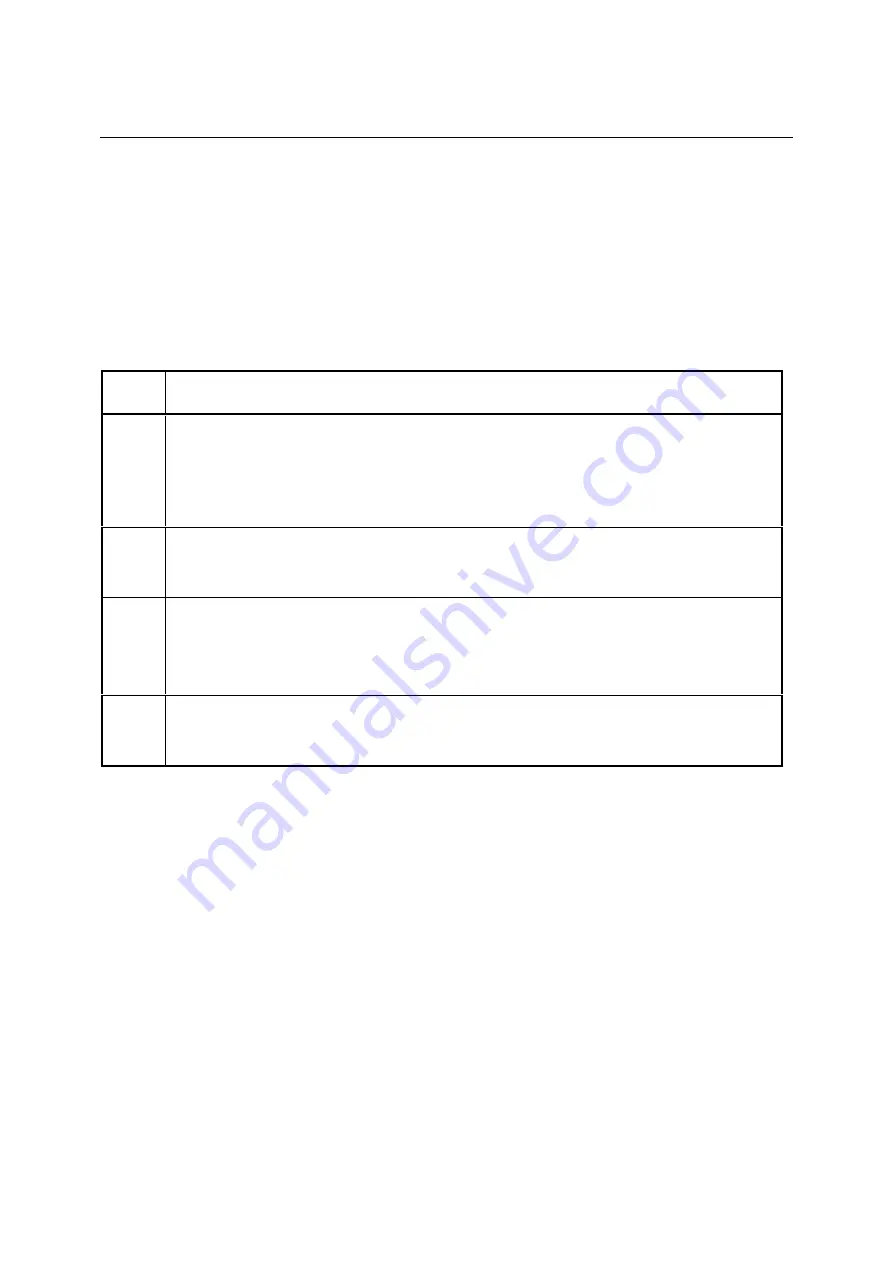

Table 8-2

Meaning of the bits used in the satus byte

Bit No.

Meaning

2

Error Queue not empty

The bit is set when an entry is made in the error queue.

If this bit is enabled by the SRE, each entry of the error queue generates a Service Request. Thus an error can

be recognized and specified in greater detail by polling the error queue. The poll provides an informative error

message. This procedure is to be recommended since it considerably reduces the problems involved with

remote control.

4

MAV bit (message available)

The bit is set if a message is available in the output buffer which can be read.

This bit can be used to enable data to be automatically read from the instrument to the controller.

5

ESB bit

Sum bit of the event status register. It is set if one of the bits in the event status register is set and enabled in

the event status enable register.

Setting of this bit implies a serious error which can be specified in greater detail by polling the event status

register.

6

MSS bit (master status smmary bit)

The bit is set if the instrument triggers a service request. This is the case if one of the other bits of this registers

is set together with its mask bit in the service request enable register SRE.