DS80C400 Network Microcontroller

83 of 96

Error Counter Interrupt Generation

The CAN module can be configured to alert the microcontroller when either 96 or 128 errors have been detected by

the transmit or receive error counters. The error-count select bit, ERCS (C0C.1), selects whether the limit is 96

(ERCS = 0) or 128 (ERCS = 1) errors. When the error limit is exceeded, the CAN error-count exceeded bit CECE

(C0S.6) is set. If the ERIE, C0IE, and EA SFR bits are configured, an interrupt is generated. If the ERCS bit is set,

the device generates an interrupt when the CECE bit is set or cleared, if the interrupt is enabled.

Bit Timing

Bit timing of the CAN transmission can be adjusted per the CAN 2.0B specification. The CAN 0 bus timing register

zero (C0BT0), located in the control/status/mask register block in MOVX memory, controls the PHASE_SEG1 and

PHASE_SEG2 time segments and the baud rate prescaler (BPR5–BPR0). The CAN 0 bus timing register one

(C0BT1) contains the controls for the sampling rate and the number of clock cycles assigned to the Phase

Segment 1 and 2 portions of the nominal bit time. The values of both of the bus timing registers are automatically

loaded into the CAN controller following each software change of the SWINT bit from a 1 to a 0 by the

microcontroller. The bit timing parameters must be set before starting operation of the CAN controller. These

registers are modifiable only during a software initialization, (SWINT = 1), when the CAN controller is

not

in a bus-

off mode, and after the removal of a system reset or a CAN reset. To avoid unpredictable behavior of the CAN

controller, the software cannot clear the SWINT bit when TSEG1 and TSEG2 are both cleared to 0.

1-Wire Bus Master

The DS80C400 incorporates a 1-Wire bus master to support communication to external 1-Wire devices. The bus

master provides complete control of the 1-Wire bus and coordinates transmit (Tx)/receive (Rx) activities with

minimal supervision by the CPU. All timing and control sequences for the bus are generated within the bus master.

Communication between the CPU and the bus master is accomplished through read/write access of the 1-Wire

master address (OWMAD; EEh) and 1-Wire master data (OWMDR; EFh) SFRs. When 1-Wire bus activity

generates a condition that requires servicing by the CPU, the bus master sets the appropriate status bit to create

an interrupt request to the CPU. If the 1-Wire bus master interrupt source has been enabled, the CPU services the

request according to the priority that has been assigned. The 1-Wire bus master supports bit banging, search ROM

accelerator, and overdrive modes. Detailed operation of the 1-Wire bus is described in

The Book of iButton

Standards

(

www.maxim-ic.com/iButtonBook

).

Communicating with the Bus Master

The microcontroller interface to the 1-Wire bus master is through two SFRs, 1-Wire master address (OWMAD;

EEh), and 1-Wire master data (OWMDR; EFh). These two registers allow read/write access of the six internal

registers of the 1-Wire bus master. The internal registers provide a means for the CPU to configure and control

transmit/receive activity through the bus master.

The three least significant bits (A2:A0) of the OWMAD SFR specify the address of the internal register to be

accessed. The OWMDR SFR is used for read/write access to the implemented bits of the specified internal

register. All internal registers are read/write accessible except the interrupt flag register (xxxxx010b), which allows

only read access to interrupt status flags. It should also be noted that all writes to the Tx/Rx buffer register

(xxxxx001b) are directed to the Tx buffer and all reads retrieve data from the Rx buffer. The 1-Wire bus master

internal register map is shown in

Table 22

.

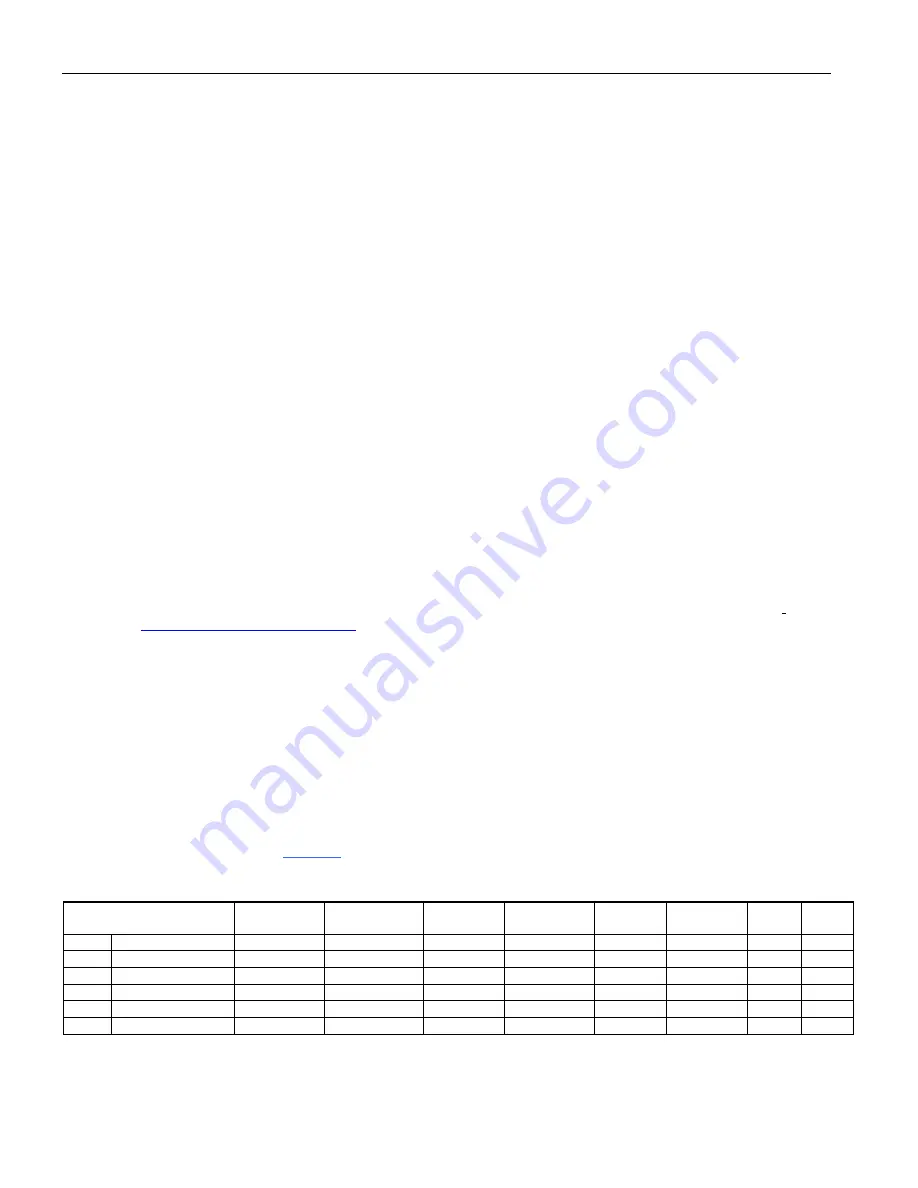

Table 22. 1-Wire Bus Master Internal Register Map

REGISTER ADDRESS

*

/

FUNCTION

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

000 Command

—

—

—

— OW_IN FOW SRA

1WR

001 Tx/Rx

Buffer

D7

D6

D5

D4

D3

D2 D1 D0

010 Interrupt

Flag OW_LOW

OW_SHORT RSRF

RBF

TEMT TBE PDR PD

011 Interrupt

Enable EOWL

EOWSH

ERSF

ERBF

ETMT ETBE

— EPD

100 Clock

Divisor CLK_EN

—

—

DIV2

DIV1 DIV0 PRE1

PRE0

101

Control

EOWMI

OD

BIT_CTL STP_SPLY STPEN EN_FOW PPM LLM

*Logic states represented by A2:A0 other than those listed in the table are considered to be invalid addresses and are not supported by the bus

master. When OWMAD contains an invalid address, reads of OWMDR return invalid data, and writes to OWMDR do not change the internal

register contents

.

Содержание DS80C400

Страница 6: ...DS80C400 Network Microcontroller 6 of 96...

Страница 7: ...DS80C400 Network Microcontroller 7 of 96...

Страница 15: ...DS80C400 Network Microcontroller 15 of 96...

Страница 16: ...DS80C400 Network Microcontroller 16 of 96 l...

Страница 22: ...DS80C400 Network Microcontroller 22 of 96 OW PIN TIMING...