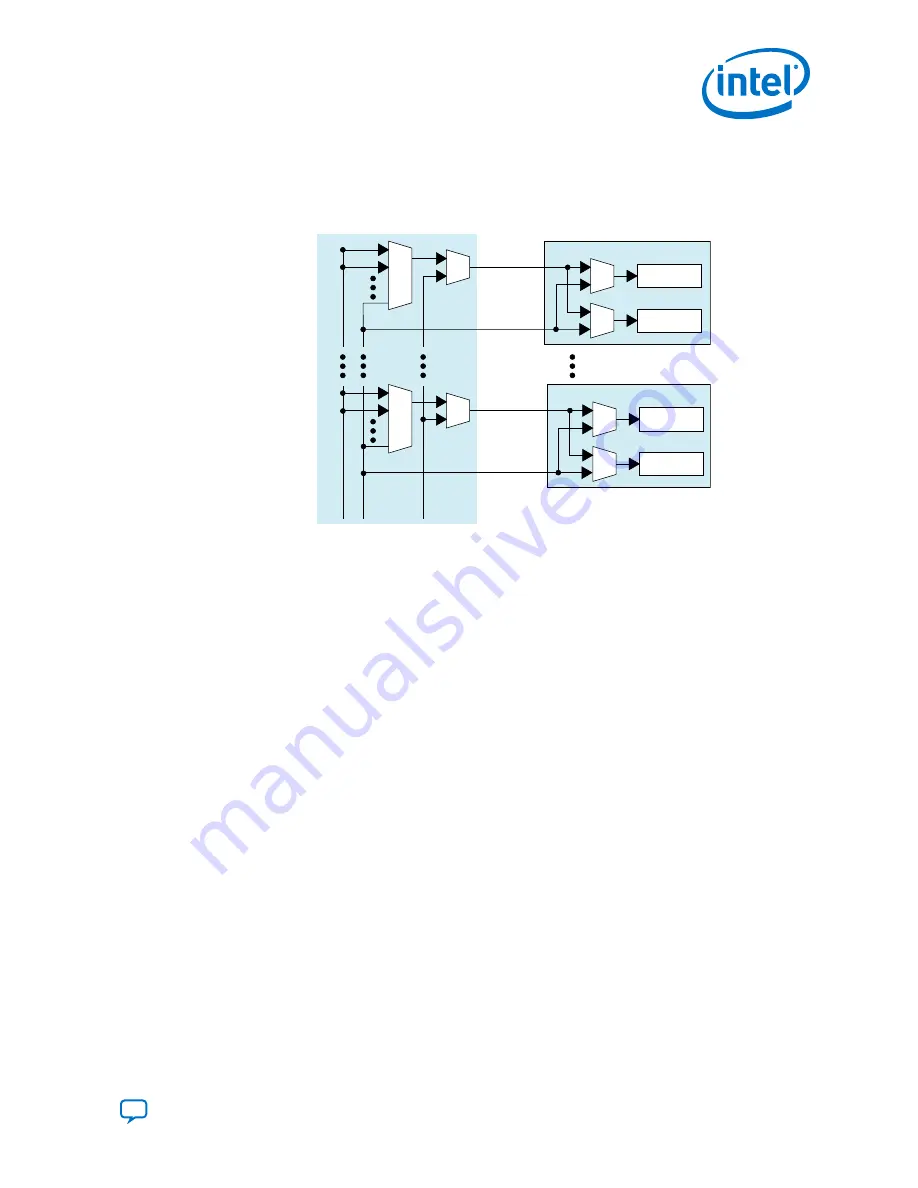

dedicated clocking resources. Muxing options allow you to select the desired external

reference clock pin to drive the individual clock input ports for each PMA channel. The

block diagram below demonstrates the muxing capability.

Figure 33.

Dynamically Selected Reference Clocks

Transmitter

Receiver

Channel 0

Transmitter

Receiver

Channel 23

re

fclk[0]

refclk_in_A

re

fclk[1]

re

fclk[8:2]

refclk_in_B

refclk_in_A

refclk_in_B

For more details, refer to Clock Network.

3.1.1. Transmitter PMA

The transmitter data path of the PMA comprises of a transmitter buffer (TX Buffer),

transmitter equalizer (TX EQ), and a serializer driven by a clock network dedicated to

each transceiver channel.

Parallel data received from the EHIP_LANE, EHIP_CORE, RS-FEC, and PMA Direct is

serialized by the serializer. This serialized data is de-emphasized to compensate for

the intersymbol interference (ISI) losses using an equalizer. The transmitter buffer at

the end of the PMA data path shapes the signal and drives the serialized data off the

chip.

3.1.1.1. High Speed Differential Transmitter

The transmitter buffer includes the following circuitry:

•

High speed transmitter line buffer

•

Transmitter equalizer

3.1.1.1.1. High Speed Transmitter Line Buffer

The transmitter differential I/O buffer converts the serialized bit stream to an electrical

signal suitable for transmission across a cable or PCB channel. The Attenuation

parameter controls the transmitter swing strength, and pre-tap/post-tap cursors help

shape the transmitter output waveform.

On power-up reset and FPGA device configuration, the transceiver supply voltage is

driven on the TX lines. During this state, both the transmitter and TX buffer are

disabled. The TX buffer is in tristate during the start-up sequence. When both the

3. Intel Stratix 10 E-Tile Transceiver PHY Architecture

UG-20056 | 2019.02.04

Intel

®

Stratix

®

10 E-Tile Transceiver PHY User Guide

59