Transmitter Description

User Manual

45

STEL-2176

Symbol Mapper Block

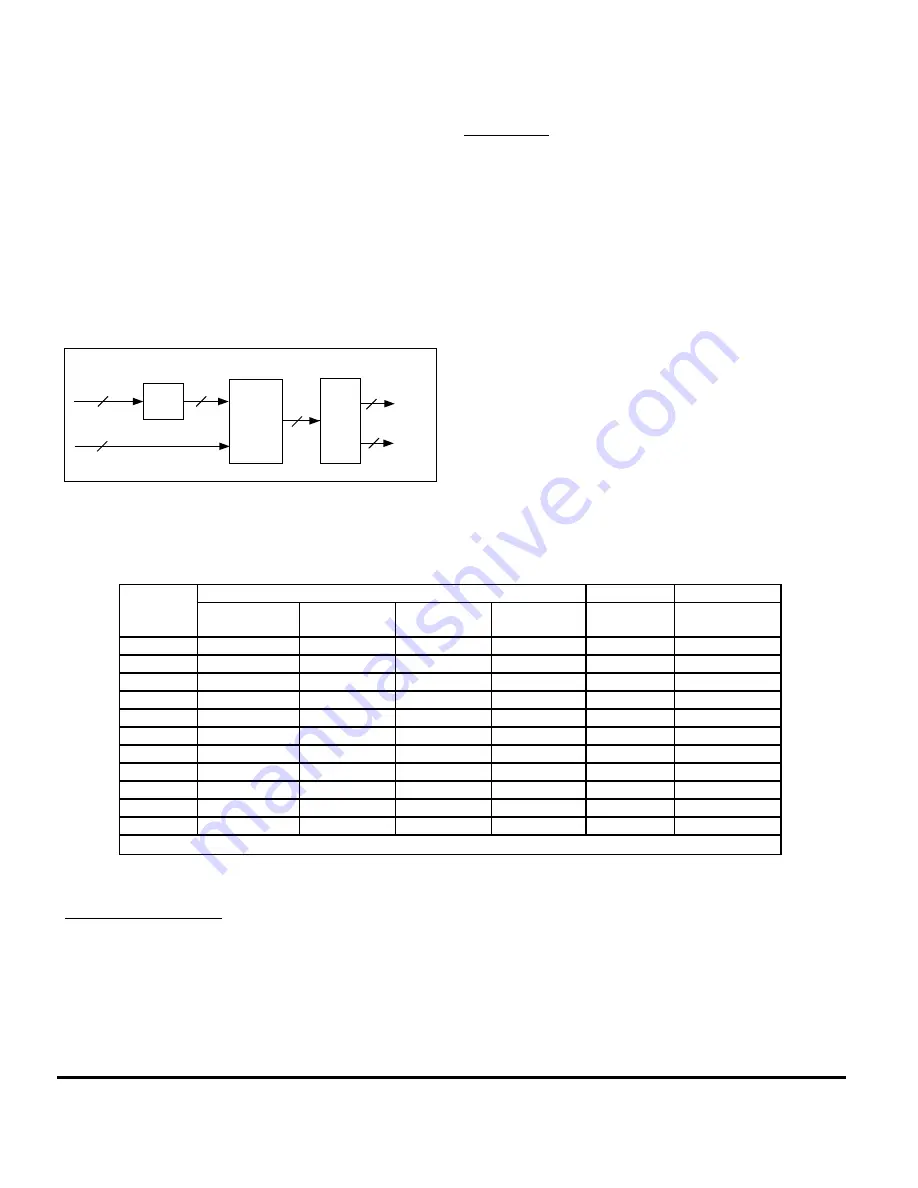

The Symbol Mapper Block (Figure 28) maps the serial

data bits output by the Bit Encoder Block to symbols,

differentially encodes the symbols, and (in 16QAM)

maps the symbols to one of five constellations. The

Symbol Mapper Block functions are modulation

dependent. The modulation mode also defines the

number of bits per symbol. The Symbol Mapper Block

outputs 2 bits for each symbol to each of the two

Nyquist (FIR) Filters.

ENCODED

SERIAL DATA

I[1:0]

**

Q[1:0]

**

I[1:0]

*

Q[1:0]

*

I[1:0]

Q[1:0]

4

Bit

Mapper

Differential

Encoder

4

2

Symbol

Mapper

2

1

TXDIFFEN

1

WCP 53810.c-12/2/97

Figure 28. Mapping Block Functional Diagram

Bit Mapper

The Bit Mapper receives serial data and maps the serial

data bits to output symbol bits (I

1

**

, I

0

**

, Q

1

**

, and Q

0

**

).

There are four output bits per symbol even in BPSK and

QPSK modes. In BPSK, all bits are set equal to each

other. In QPSK, each input symbol bit drives a pair of

output bits. The four symbol bits are routed to the

Differential Encoder in parallel.

For BPSK modulation, each bit (symbol = b

0

) of the

input serial data stream is mapped directly to I

1

**

, Q

1

**

,

I

0

**

, and Q

0

* *

(i.e., I

1

**

= I

0

* *

= Q

1

**

= Q

0

**

= b

0

). Thus, bit

mapping has no affect on the respective value of the

symbolÕs four bits, as shown in Table 38.

For QPSK modulation, each pair of bits (a dibit) forms a

symbol (b

0

b

1 )

. The QPSK dibit is mapped so that

I

1

**Ê

=ÊI

0

**

and Q

1

**

=

Q

0

**,

as shown in Table 38.

For 16QAM, every four bits (a nibble) forms a symbol

(b

0

b

1

b

2

b

3

). The 16QAM nibble is mapped to I

1

**

, Q

1

**

, I

0

**

,

and Q

0

**

, as shown in Table 38.

Table 38. Bit Mapping Options

Bit-To-Symbol Mapping

Bit Mapping

Mod Mode

Mode

b

0

b

1

b

2

b

3

Register 2D

bits 6-4

Register 2C bits

3,2

BPSK

I

1

**

Q

1

**

I

0

**

Q

0

**

N/A

N/A

N/A

XXX

1X

QPSK

I

1

**

I

0

**

Q

1

**

Q

0

**

N/A

N/A

XX0

00

QPSK

Q

1

**

Q

0

**

I

1

**

I

0

**

N/A

N/A

XX1

00

16QAM

I

1

**

I

0

**

Q

1

**

Q

0

**

000

01

16QAM

Q

1

**

Q

0

**

I

1

**

I

0

**

001

01

16QAM

I

0

**

I

1

**

Q

0

**

Q

1

**

010

01

16QAM

Q

0

**

Q

1

**

I

0

**

I

1

**

011

01

16QAM

I

1

**

Q

1

**

I

0

**

Q

0

**

100

01

16QAM

Q

1

**

I

1

**

Q

0

**

I

0

**

101

01

16QAM

I

0

**

Q

0

**

I

1

**

Q

1

**

110

01

16QAM

Q

0

**

I

0

**

Q

1

**

I

1

**

111

01

Note: b

0

is the first serial data bit to arrive at the Bit Mapper

Differential Encoder

The Differential Encoder encodes the bits (i.e., I

1

**

, I

0

**

,

Q

1

**

, and Q

0

* *

) of each symbol received from the Bit

Mapper to determine the output bit values (i.e., I

1

*

, Q

1

*

,

I

0

*

, and Q

0

*

), which are routed to the Symbol Mapper.

The differential encoder can be either enabled or

bypassed under the control of either a register bit or a

user supplied control signal (TXDIFFEN). The selection

between user input pin control or register control is

made in another register bit, as shown in Table 39.