IDT SMBus Interfaces

Master SMBus Interface

PES12N3 User Manual

7 - 8

June 7, 2006

Notes

Programming the Serial EEPROM

The serial EEPROM may be programmed prior to board assembly or in-system via the slave SMBus

interface or a PCIe® root. Programming the serial EEPROM via the slave SMBus is described in section

Serial EEPROM Read or Write Operation on page 7-12. A PCIe root may read and write the serial

EEPROM by performing configuration read and write transactions to the port A Serial EEPROM Interface

(PA_EEPROMINTF) register.

To read a byte from the serial EEPROM, the root should configure the Address (ADDR) field in the

PA_EEPROMINTF register with the byte address of the serial EEPROM location to be read and the Opera-

tion (OP) field to “read.” The Busy (BUSY) bit should then be checked. If the EEPROM is not busy, then the

read operation may be initiated by performing a write to the Data (DATA) field. When the serial EEPROM

read operation completes, the Done (DONE) bit in the PA_EEPROMINTF register is set and the busy bit is

cleared. When this occurs, the DATA field contains the byte data of the value read from the serial EEPROM.

To write a byte to the serial EEPROM, the root should configure the ADDR field with the byte address of

the serial EEPROM location to be written and set the OP field to “write.” If the serial EEPROM is not busy

(i.e., the BUSY bit is cleared), then the write operation may be initiated by writing the value to be written to

the DATA field. When the write operation completes, the DONE bit is set and the busy bit is cleared.

Initiating a serial EEPROM read or write operation when the BUSY bit is set produces undefined results.

SMBus errors may occur when accessing the serial EEPROM. If an error occurs, then it is reported in the

port A SMBus Status (PA_SMBUSSTS) register. Software should check for errors before and after each

serial EEPROM access.

Hot-Plug I/O Expander

The PES12N3 utilizes an external SMBus/I2C-bus I/O expander connected to the master SMBus inter-

face for hot-plug related signals associated with downstream ports. See section Hot-Plug I/O Expander on

page 6-3 for information on the operation of the hot-plug I/O expander.

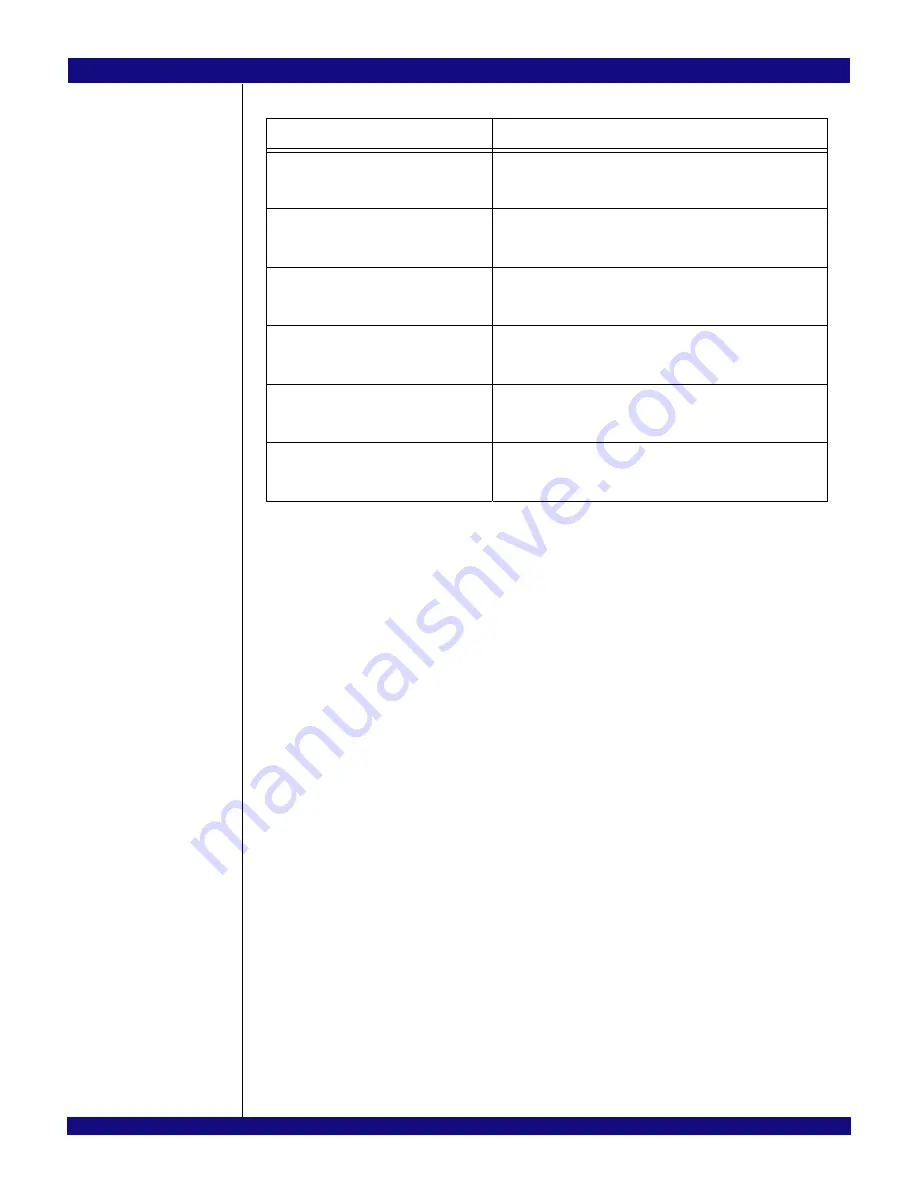

Error

Action Taken

Configuration Done Sequence checksum

mismatch with that computed by the

PES12N3

- Set RSTHALT bit in PA_SWCTL register

- ICSERR bit is set in the PA_SMBUSSTS register

- Abort initialization, set DONE bit in the PA_SMBUSSTS register

Serial EERPOM address roll-over from

0xFFFF to 0x0000

- Set RSTHALT bit in PA_SWCTL register

- ICSERR bit is set in the PA_SMBUSSTS register

- Abort initialization, set DONE bit in the PA_SMBUSSTS register

Invalid configuration block type

(only invalid type is 0x2)

- Set RSTHALT bit in PA_SWCTL register

- ICSERR bit is set in the PA_SMBUSSTS register

- Abort initialization, set DONE bit in the PA_SMBUSSTS register

An unexpected NACK is observed during a

master SMBus transaction

- Set RSTHALT bit in PA_SWCTL register

- NAERR bit is set in the PA_SMBUSSTS register

- Abort initialization, set DONE bit in the PA_SMBUSSTS register

Master SMBus interface loses 16 consecu-

tive arbitration attempts

- Set RSTHALT bit in PA_SWCTL register

- LAERR bit is set in the PA_SMBUSSTS register

- Abort initialization, set DONE bit in the PA_SMBUSSTS register

A misplaced START or STOP condition is

detected by the master SMBus interface

- Set RSTHALT bit in PA_SWCTL register

- OTHERERR bit is set in the PA_SMBUSSTS register

- Abort initialization, set DONE bit in the PA_SMBUSSTS register

Table 7.6 Serial EEPROM Initialization Errors

Содержание 89HPES12N3

Страница 10: ...IDT Table of Contents PES12N3 User Manual iv June 7 2006 Notes...

Страница 14: ...IDT List of Figures PES12N3 User Manual viii June 7 2006 Notes...

Страница 36: ...IDT Clocking Reset and Initialization Reset PES12N3 User Manual 2 8 June 7 2006 Notes...

Страница 40: ...IDT Link Operation Slot Power Limit Support PES12N3 User Manual 3 4 June 7 2006 Notes...

Страница 50: ...IDT Switch Operation Switch Core Errors PES12N3 User Manual 4 10 June 7 2006 Notes...

Страница 54: ...IDT Power Management Active State Power Management PES12N3 User Manual 5 4 June 7 2006 Notes...

Страница 62: ...IDT Hot Plug and Hot Swap Hot Swap PES12N3 User Manual 6 8 June 7 2006 Notes...

Страница 78: ...IDT SMBus Interfaces Slave SMBus Interface PES12N3 User Manual 7 16 June 7 2006 Notes...

Страница 142: ...IDT Transparent Mode Operation Generic PCI to PCI Bridge Register Definition PES12N3 User Manual 9 62 June 7 2006 Notes...

Страница 148: ...IDT Test and Debug SerDes Test Clock PES12N3 User Manual 10 6 June 7 2006...

Страница 158: ...IDT JTAG Boundary Scan Usage Considerations PES12N3 User Manual 11 10 June 7 2006 Notes...