Rev. 1.10

42

November 04, 2019

Rev. 1.10

43

November 04, 2019

HT45F5Q-3

Battery Charger Flash MCU

HT45F5Q-3

Battery Charger Flash MCU

SLOW Mode to FAST Mode Switching

In SLOW mode the system clock is derived from f

SUB

. When system clock is switched back to the

FAST mode from f

SUB

, the CKS2~CKS0 bits should be set to “000”~“110” and then the system

clock will respectively be switched to f

H

~f

H

/64.

However, if f

H

is not used in SLOW mode and thus switched off, it will take some time to re-

oscillate and stabilise when switching to the FAST mode from the SLOW Mode. This is monitored

using the HIRCF bit in the HIRCC register. The time duration required for the high speed system

oscillator stabilization is specified in the System Start Up Time Characteristics.

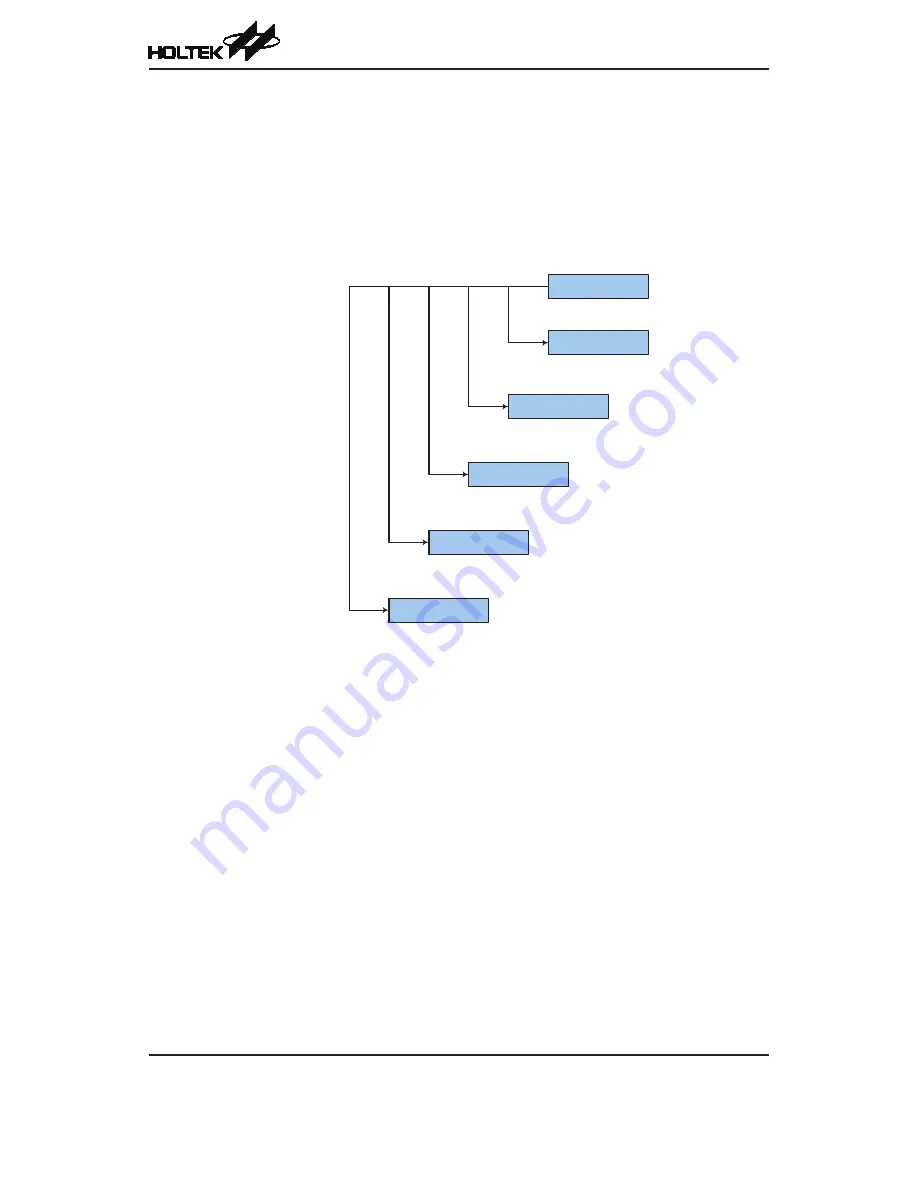

FAST Mode

SLOW Mode

CKS2~CKS0=000~110

SLEEP Mode

FHIDEN=0, FSIDEN=0

HALT instruction is executed

IDLE0 Mode

FHIDEN=0, FSIDEN=1

HALT instruction is executed

IDLE1 Mode

FHIDEN=1, FSIDEN=1

HALT instruction is executed

IDLE2 Mode

FHIDEN=1, FSIDEN=0

HALT instruction is executed

Entering the SLEEP Mode

There is only one way for the device to enter the SLEEP Mode and that is to execute the “HALT”

instruction in the application program with both the FHIDEN and FSIDEN bits in the SCC register

equal to “0”. In this mode all the clocks and functions will be switched off except the WDT function.

When this instruction is executed under the conditions described above, the following will occur:

•

The system clock will be stopped and the application program will stop at the “HALT” instruction.

•

The Data Memory contents and registers will maintain their present condition.

•

The I/O ports will maintain their present conditions.

•

In the status register, the Power Down flag, PDF, will be set and the Watchdog time-out flag, TO,

will be cleared.

•

The WDT will be cleared and resume counting if the WDT function is enabled. If the WDT

function is disabled, the WDT will be cleared and then stopped.