RESET

3-11

n

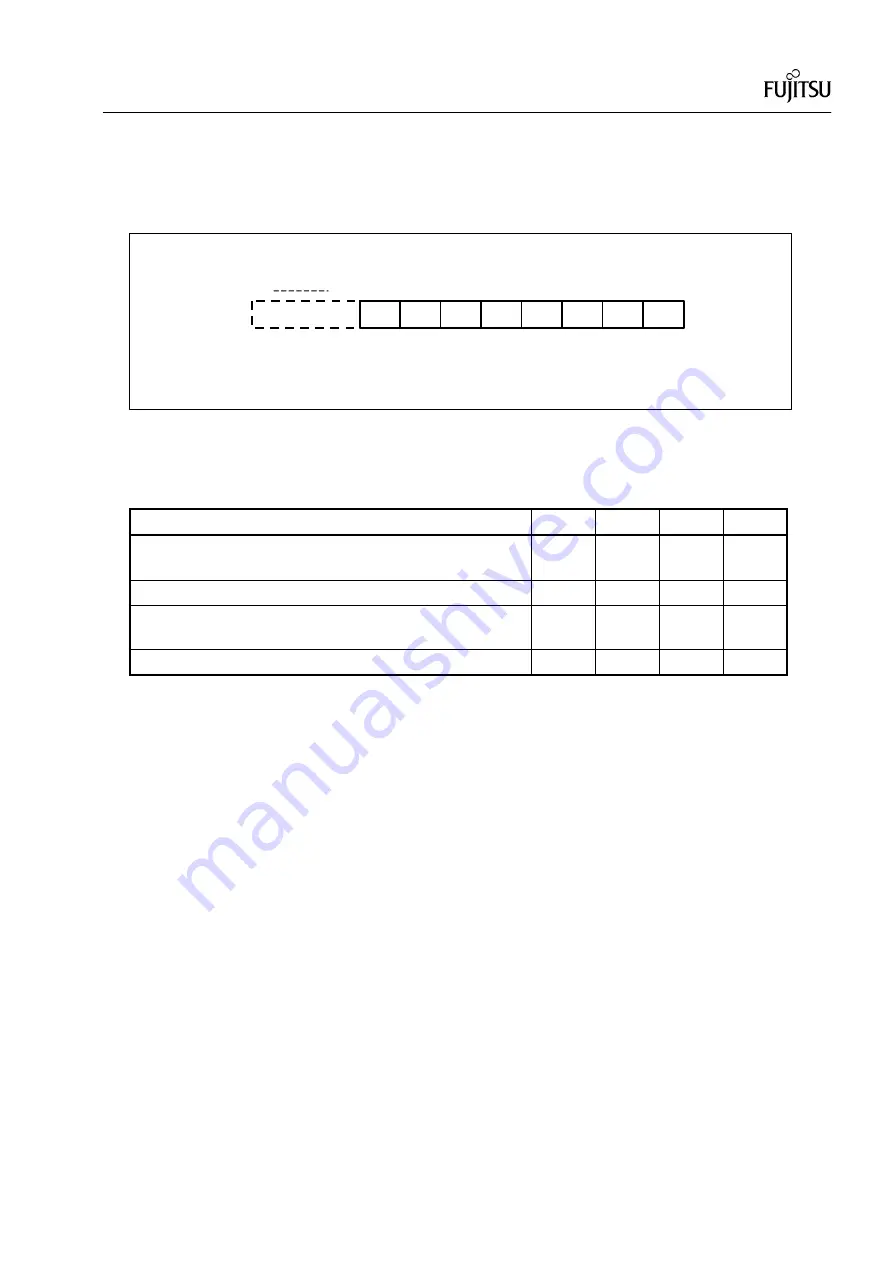

Correspondence of reset factor bit and reset factor

Figure 3.8

shows the configuration of the reset factor bit of the watchdog timer control register (WDTC), and

the

Table 3-4

shows the correspondence of the reset bit value and the reset factor. For detail, see

Section

7.1

.

Fig. 3.8 Configuration of Reset Factor Bit (Watchdog Timer Control Register)

Table 3-4 Correspondence of Reset Factor Bit Value and Reset Factor

Reset Factor

PONR

WRST

ERST

SRST

Power-on reset request

Low voltage detection reset request

*1

1

X

X

X

Reset request by watchdog timer overflow

*

1

*

*

External reset request from RSTX pin

CPU Operation detection reset request

*2

*

*

1

*

Software reset request

*

*

*

1

* :

The previous state is held

X :

Undefined

*1 :

At a low voltage detection reset request, the LVRF bit of the low voltage/CPU operation detection

reset control register (LVRC) is also set to 1.

*2 :

At a CPU operation detection reset request, the CPUF bit of the low voltage/CPU operation

detection reset control register (LVRC) is also set to 1.

n

Notes on reset factor bit

•

At plural reset factor

When plural reset factors occur, the corresponding reset factor bits of the watchdog timer control register

(WDTC) are set to “1”. For example, when an external reset request from the RSTX pin and a watchdog

timer overflow occur simultaneously, the ERST and WRST bits are set to “1”.

•

Power-on reset

At power-on reset, the PONR bit is set to “1”, and reset factor bits other than the PONR bit are undefined.

Consequently, the software must ignore reset factor bits other than the PONR bit when the PONR bit is “1”.

•

Clearing reset factor bit

The reset factor bits are cleared only when the watchdog timer control register (WDTC) is read. Even

when another reset is caused by an other factor afterward, the flag set at the bit corresponding to each

reset factor is not cleared (flag remains 1).

Note:

When the power is turned on, under condition that no power-on reset occurs, the value of the WDTC

register is not assured.

Address bit 15

bit 8

bit 7

bit 6

bit 5

bit 4

bit 3

bit 2

bit 1

bit 0

R

—

R

R

R

W

W

W

Initial value

Watchdog timer control register (WDTC)

R : Read only

W : Write only

X : Undefined

(TBTC)

PONR

—

WRST ERST SRST WTE

WT1

WT0

0000A8

H

X-XXX111

B

Содержание MB90420/5 (A) Series

Страница 2: ...ii ...

Страница 24: ...MB90420 5 A SERIES F2 MC 16LX FAMILY 16 BIT MICROCONTROLLERS HARDWARE MANUAL 1 2 ...

Страница 42: ...MB90420 5 A SERIES F2 MC 16LX FAMILY 16 BIT MICROCONTROLLERS HARDWARE MANUAL 2 2 ...

Страница 76: ...MB90420 5 A SERIES F2 MC 16LX FAMILY 16 BIT MICROCONTROLLERS HARDWARE MANUAL 2 36 ...

Страница 78: ...MB90420 5 A SERIES F2 MC 16LX FAMILY 16 BIT MICROCONTROLLERS HARDWARE MANUAL 3 2 ...

Страница 90: ...MB90420 5 A SERIES F2 MC 16LX FAMILY 16 BIT MICROCONTROLLERS HARDWARE MANUAL 4 2 ...

Страница 102: ...MB90420 5 A SERIES F2 MC 16LX FAMILY 16 BIT MICROCONTROLLERS HARDWARE MANUAL 4 14 ...

Страница 104: ...MB90420 5 A SERIES F2 MC 16LX FAMILY 16 BIT MICROCONTROLLERS HARDWARE MANUAL 5 2 ...

Страница 126: ...MB90420 5 A SERIES F2 MC 16LX FAMILY 16 BIT MICROCONTROLLERS HARDWARE MANUAL 5 24 ...

Страница 128: ...MB90420 5 A SERIES F2 MC 16LX FAMILY 16 BIT MICROCONTROLLERS HARDWARE MANUAL 6 2 ...

Страница 165: ...7 1 Mode Setting 7 3 7 2 Mode Pins MD2 to MD0 7 4 7 3 Mode Data 7 5 7 MODE SETTING ...

Страница 166: ...MB90420 5 A SERIES F2 MC 16LX FAMILY 16 BIT MICROCONTROLLERS HARDWARE MANUAL 7 2 ...

Страница 172: ...MB90420 5 A SERIES F2 MC 16LX FAMILY 16 BIT MICROCONTROLLERS HARDWARE MANUAL 8 2 ...

Страница 224: ...MB90420 5 A SERIES F2 MC 16LX FAMILY 16 BIT MICROCONTROLLERS HARDWARE MANUAL 9 2 ...

Страница 244: ...MB90420 5 A SERIES F2 MC 16LX FAMILY 16 BIT MICROCONTROLLERS HARDWARE MANUAL 10 2 ...

Страница 270: ...MB90420 5 A SERIES F2 MC 16LX FAMILY 16 BIT MICROCONTROLLERS HARDWARE MANUAL 11 2 ...

Страница 286: ...MB90420 5 A SERIES F2 MC 16LX FAMILY 16 BIT MICROCONTROLLERS HARDWARE MANUAL 12 2 ...

Страница 326: ...MB90420 5 A SERIES F2 MC 16LX FAMILY 16 BIT MICROCONTROLLERS HARDWARE MANUAL 13 2 ...

Страница 338: ...MB90420 5 A SERIES F2 MC 16LX FAMILY 16 BIT MICROCONTROLLERS HARDWARE MANUAL 14 2 ...

Страница 353: ...LCD CONTROLLER DRIVER 14 17 ...

Страница 365: ...LCD CONTROLLER DRIVER 14 29 ...

Страница 367: ...MB90420 5 A SERIES F2 MC 16LX FAMILY 16 BIT MICROCONTROLLERS HARDWARE MANUAL 15 2 ...

Страница 377: ...MB90420 5 A SERIES F2 MC 16LX FAMILY 16 BIT MICROCONTROLLERS HARDWARE MANUAL 16 2 ...

Страница 397: ...MB90420 5 A SERIES F2 MC 16LX FAMILY 16 BIT MICROCONTROLLERS HARDWARE MANUAL 17 2 ...

Страница 400: ...18 1 Overview of Timepiece Timer 18 3 18 2 Timepiece Timer Registers 18 4 18 TIMEPIECE TIMER ...

Страница 401: ...MB90420 5 A SERIES F2 MC 16LX FAMILY 16 BIT MICROCONTROLLERS HARDWARE MANUAL 18 2 ...

Страница 409: ...MB90420 5 A SERIES F2 MC 16LX FAMILY 16 BIT MICROCONTROLLERS HARDWARE MANUAL 19 2 ...

Страница 436: ...20 1 Overview of Sound Generator 20 3 20 2 Sound Generator Registers 20 4 20 SOUND GENERATOR ...

Страница 437: ...MB90420 5 A SERIES F2 MC 16LX FAMILY 16 BIT MICROCONTROLLERS HARDWARE MANUAL 20 2 ...

Страница 445: ...MB90420 5 A SERIES F2 MC 16LX FAMILY 16 BIT MICROCONTROLLERS HARDWARE MANUAL 20 10 ...

Страница 446: ...21 1 Overview of ROM Correction 21 3 21 2 Application Example of ROM Correction 21 6 21 ROM CORRECTION ...

Страница 447: ...MB90420 5 A SERIES F2 MC 16LX FAMILY 16 BIT MICROCONTROLLERS HARDWARE MANUAL 21 2 ...

Страница 455: ...MB90420 5 A SERIES F2 MC 16LX FAMILY 16 BIT MICROCONTROLLERS HARDWARE MANUAL 21 10 ...

Страница 457: ...MB90420 5 A SERIES F2 MC 16LX FAMILY 16 BIT MICROCONTROLLERS HARDWARE MANUAL 22 2 ...

Страница 461: ...MB90420 5 A SERIES F2 MC 16LX FAMILY 16 BIT MICROCONTROLLERS HARDWARE MANUAL 23 2 ...

Страница 503: ...MB90420 5 A SERIES F2 MC 16LX FAMILY 16 BIT MICROCONTROLLERS HARDWARE MANUAL 23 44 ...

Страница 505: ...MB90420 5 A SERIES F2 MC 16LX FAMILY 16 BIT MICROCONTROLLERS HARDWARE MANUAL 24 2 ...

Страница 513: ...MB90420 5 A SERIES F2 MC 16LX FAMILY 16 BIT MICROCONTROLLERS HARDWARE MANUAL 24 10 ...

Страница 515: ...MB90420 5 A SERIES F2 MC 16LX FAMILY 16 BIT MICROCONTROLLERS HARDWARE MANUAL 25 2 ...

Страница 541: ...MB90420 5 A SERIES F2 MC 16LX FAMILY 16 BIT MICROCONTROLLERS HARDWARE MANUAL 26 2 ...