Document type:

Title:

Revision date:

Revision:

User's Manual (MUT)

Mod. V1724 8 Channel 14bit - 100MS/s Digitizer

06/11/2007

7

NPO:

Filename:

Number of pages:

Page:

00103/05:V1724x.MUTx/07 V1724_REV7.DOC

63

39

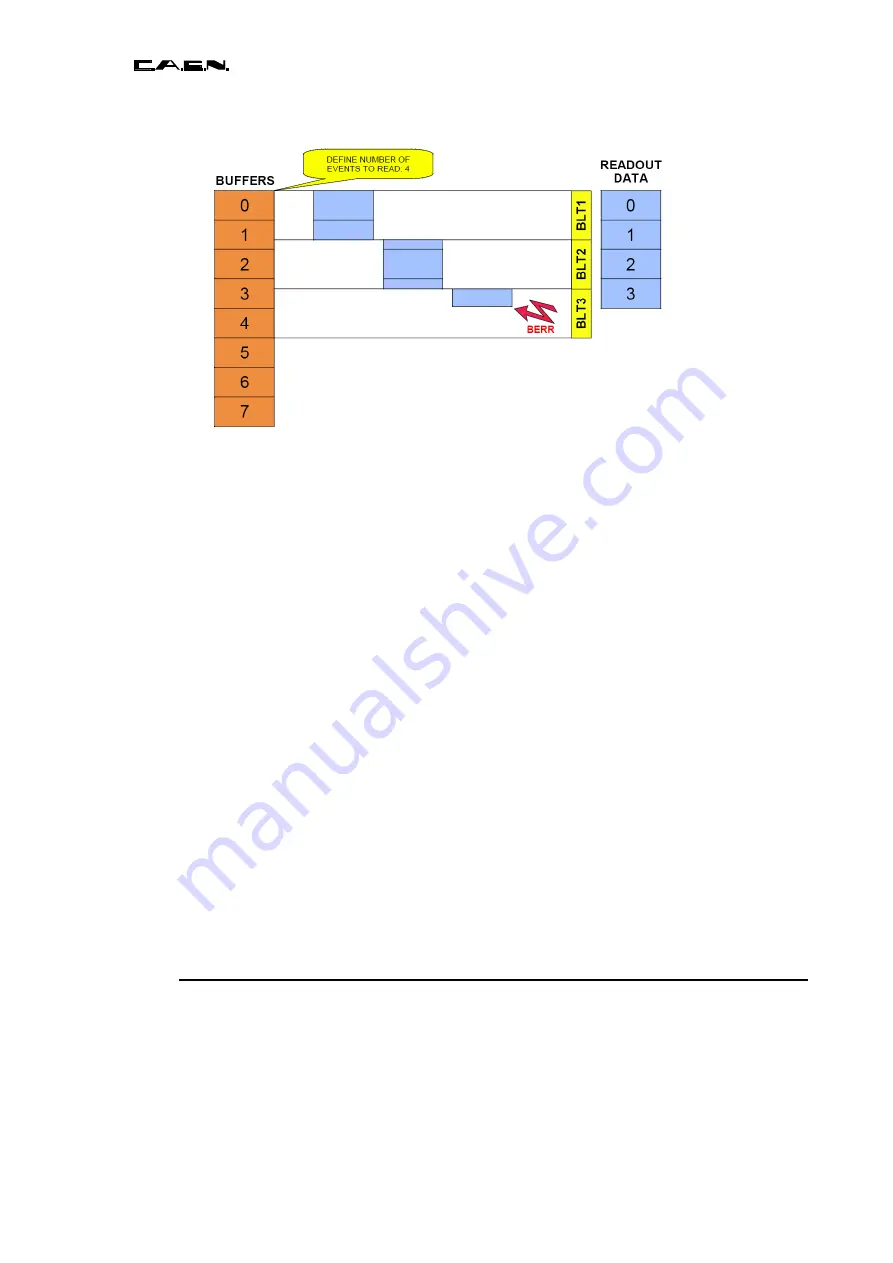

Block size = 1024 bytes

BERR = enabled

BLT size = 16384 bytes

N = 4

Fig. 3.23: Example of BLT readout

Since some 64 bit CPU’s cut off the last 32 bit word of a transferred block, if the number

of words composing such block is odd, it is necessary to add a dummy word (which has

then to be removed via software) in order to avoid data loss. This can be achieved by

setting the ALIGN64 bit in the VME Control register (see § 4.30).

MBLT64 cycle is similar to the BLT32 cycle, except that the address and data lines are

multiplexed to form 64 bit address and data buses.

The 2eVME allows to achieve higher transfer rates thanks to the requirement of only two

edges of the two control signals (DS and DTACK) to complete a data cycle.

3.12.1.3.

CHAINED BLOCK TRANSFER D32/D64

The V1724 allows to readout events from more daisy chained boards (Chained Block

Transfer mode).

The technique which handles the CBLT is based on the passing of a token between the

boards; it is necessary toverify that the used VME crate supports such cycles.

Several contiguous boards, in order to be daisy chained, must be configured as “first”,

“intermediate” or “last” via MCST Base Address and Control Register (see § 4.38

). A

common Base Address is then defined via the same register; when a BLT cycle is

executed at the address CBL 0x0000 ÷ 0x0FFC, the “first” board starts to

transfer its data, driving DTACK properly; once the transfer is completed, the token is

passed to the second board via the IACKIN-IACKOUT lines of the crate, and so on until

the “last” board, which completes the data transfer and asserts BERR (which has to be

enabled): the Master then ends the cycle and the slave boards are rearmed for a new

acquisition.

If the size of the BLT cycle is smaller than the events size, the board which has the token

waits for another BLT cycle to begin (from the point where the previous cycle has ended).

3.12.2.

Random readout (to be implemented)

Events can be readout partially (not necessarily starting from the first available) and are

not erased from the memories, unless a command is performed. In order to perform the

random readout it is necessary to execute an

Event Block Request

via VME.

Indicating the event to be read (page number = 12 bit datum), the offset of the first word

to be read inside the event (12 bit datum) and the number of words to be read (size = 10

bit datum). At this point the data space can be read, starting from the header (which