355

4317I–AVR–01/08

AT90PWM2/3/2B/3B

3.

PSC : the Balance Flank Width Modulation is done On-Time 1 rather than On-Time 0

(correction of figures)

4.

Updated

“Maximum Speed vs. VCC” on page 303

(formulas are removed)

5.

Update of the

33.8

Changes from 4317H to 4317I

1.

Updated

2.

Updated

“Device Clocking Options Select AT90PWM2B/3B” on page 31

3.

Updated

“Start-up Times when the PLL is selected as system clock” on page 35

4.

Updated

“ADC Noise Canceler” on page 241

5.

Updated

“ADC Auto Trigger Source Selection for non amplified conversions” on page

.

6.

Added

“ADC Auto Trigger Source Selection for amplified conversions” on page 250

7.

Updated

8.

Updated

“Amplifier 0 Control and Status register – AMP0CSR” on page 256

9.

Updated

“AMP0 Auto Trigger Source Selection” on page 257

10. Updated

“Amplifier 1Control and Status register – AMP1CSR” on page 257

“AMP1 Auto Trigger source selection” on page 258

12. Updated DAC

(Output Impedance)

13. Updated temperature range in

“DC Characteristics” on page 300

“DC Characteristics” on page 300

15. Updated

“ADC Characteristics” on page 306

16. Updated

17. Updated

18. Updated

19. Added

“I/O Pin Input HysteresisVoltage vs. VCC” on page 323

20. Updated

“Ordering Information” on page 344

“Package Information” on page 345

.

23. Updated table on page 2.

24. Updated

“Calibrated Internal RC Oscillator” on page 33

.

25. Added

“Calibrated Internal RC Oscillator Accuracy” on page 302

26. Updated

27. Updated

28. Updated

Содержание AT90PWM2

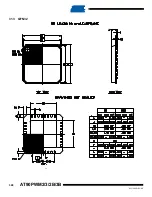

Страница 344: ...346 4317I AVR 01 08 AT90PWM2 3 2B 3B 31 1 SO24...

Страница 345: ...347 4317I AVR 01 08 AT90PWM2 3 2B 3B 31 2 SO32...

Страница 346: ...348 4317I AVR 01 08 AT90PWM2 3 2B 3B 31 3 QFN32...

Страница 347: ...349 4317I AVR 01 08 AT90PWM2 3 2B 3B...