241

4317I–AVR–01/08

AT90PWM2/3/2B/3B

If differential channels are used, the selected reference should not be closer to AV

CC

than indi-

.

21.6

ADC Noise Canceler

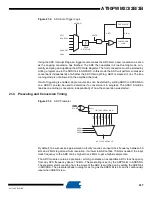

The ADC features a noise canceler that enables conversion during sleep mode to reduce noise

induced from the CPU core and other I/O peripherals. The noise canceler can be used with ADC

Noise Reduction and Idle mode. To make use of this feature, the following procedure should be

used:

a.

Make sure that the ADATE bit is reset.

b.

Make sure that the ADC is enabled and is not busy converting. Single Conversion

mode must be selected and the ADC conversion complete interrupt must be

enabled.

c.

Enter ADC Noise Reduction mode (or Idle mode). The ADC will start a conversion

once the CPU has been halted.

d.

If no other interrupts occur before the ADC conversion completes, the ADC inter-

rupt will wake up the CPU and execute the ADC Conversion Complete interrupt

routine. If another interrupt wakes up the CPU before the ADC conversion is com-

plete, that interrupt will be executed, and an ADC Conversion Complete interrupt

request will be generated when the ADC conversion completes. The CPU will

remain in active mode until a new sleep command is executed.

Note that the ADC will not be automatically turned off when entering other sleep modes than Idle

mode and ADC Noise Reduction mode. The user is advised to write zero to ADEN before enter-

ing such sleep modes to avoid excessive power consumption.

If the ADC is enabled in such sleep modes and the user wants to perform differential conver-

sions, the user is advised to switch the ADC off and on after waking up from sleep to prompt an

extended conversion to get a valid result.

21.6.1

Analog Input Circuitry

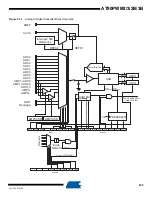

The analog input circuitry for single ended channels is illustrated in Figure 21-8. An analog

source applied to ADCn is subjected to the pin capacitance and input leakage of that pin, regard-

less of whether that channel is selected as input for the ADC. When the channel is selected, the

source must drive the S/H capacitor through the series resistance (combined resistance in the

input path).

The ADC is optimized for analog signals with an output impedance of approximately 10 k

Ω

or

less. If such a source is used, the sampling time will be negligible. If a source with higher imped-

ance is used, the sampling time will depend on how long time the source needs to charge the

S/H capacitor, with can vary widely. The user is recommended to only use low impedant sources

with slowly varying signals, since this minimizes the required charge transfer to the S/H

capacitor.

If differential gain channels are used, the input circuitry looks somewhat different, although

source impedances of a few hundred k

Ω

or less is recommended.

Signal components higher than the Nyquist frequency (f

ADC

/2) should not be present for either

kind of channels, to avoid distortion from unpredictable signal convolution. The user is advised

to remove high frequency components with a low-pass filter before applying the signals as

inputs to the ADC.

Содержание AT90PWM2

Страница 344: ...346 4317I AVR 01 08 AT90PWM2 3 2B 3B 31 1 SO24...

Страница 345: ...347 4317I AVR 01 08 AT90PWM2 3 2B 3B 31 2 SO32...

Страница 346: ...348 4317I AVR 01 08 AT90PWM2 3 2B 3B 31 3 QFN32...

Страница 347: ...349 4317I AVR 01 08 AT90PWM2 3 2B 3B...