201

4317I–AVR–01/08

AT90PWM2/3/2B/3B

The recommendations of the maximum receiver baud rate error was made under the assump-

tion that the Receiver and Transmitter equally divides the maximum total error.

There are two possible sources for the receivers baud rate error. The Receiver’s system clock

(XTAL) will always have some minor instability over the supply voltage range and the tempera-

ture range. When using a crystal to generate the system clock, this is rarely a problem, but for a

resonator the system clock may differ more than 2% depending of the resonators tolerance. The

second source for the error is more controllable. The baud rate generator can not always do an

exact division of the system frequency to get the baud rate wanted. In this case an UBRR value

that gives an acceptable low error can be used if possible.

18.9

Multi-processor Communication Mode

This mode is available only in USART mode, not in EUSART.

Setting the Multi-processor Communication mode (MPCM) bit in UCSRA enables a filtering

function of incoming frames received by the USART Receiver. Frames that do not contain

address information will be ignored and not put into the receive buffer. This effectively reduces

the number of incoming frames that has to be handled by the CPU, in a system with multiple

MCUs that communicate via the same serial bus. The Transmitter is unaffected by the MPCM

setting, but has to be used differently when it is a part of a system utilizing the Multi-processor

Communication mode.

18.9.1

MPCM Protocol

If the Receiver is set up to receive frames that contain 5 to 8 data bits, then the first stop bit indi-

cates if the frame contains data or address information. If the Receiver is set up for frames with

nine data bits, then the ninth bit (RXB8) is used for identifying address and data frames. When

the frame type bit (the first stop or the ninth bit) is one, the frame contains an address. When the

frame type bit is zero the frame is a data frame.

The Multi-processor Communication mode enables several slave MCUs to receive data from a

master MCU. This is done by first decoding an address frame to find out which MCU has been

addressed. If a particular slave MCU has been addressed, it will receive the following data

frames as normal, while the other slave MCUs will ignore the received frames until another

address frame is received.

18.9.2

Using MPCM

For an MCU to act as a master MCU, it can use a 9-bit character frame format (UCSZ = 7). The

ninth bit (TXB8) must be set when an address frame (TXB8 = 1) or cleared when a data frame

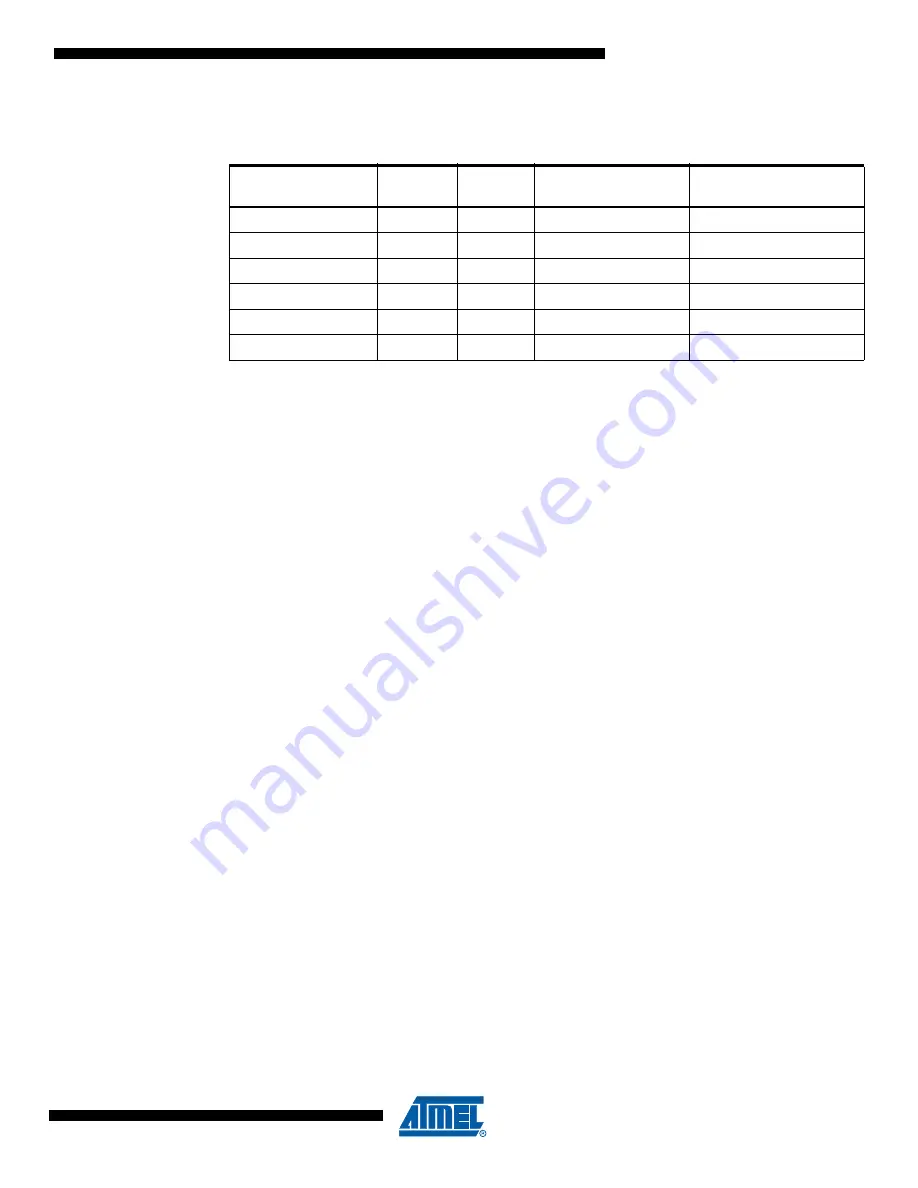

Table 18-3.

Recommended Maximum Receiver Baud Rate Error for Double Speed Mode

(U2X = 1)

D

# (Data+Parity Bit)

R

slow

(%)

R

fast

(%)

Max Total Error (%)

Recommended Max

Receiver Error (%)

5

94.12

105.66

+5.66/-5.88

± 2.5

6

94.92

104.92

+4.92/-5.08

± 2.0

7

95.52

104,35

+4.35/-4.48

± 1.5

8

96.00

103.90

+3.90/-4.00

± 1.5

9

96.39

103.53

+3.53/-3.61

± 1.5

10

96.70

103.23

+3.23/-3.30

± 1.0

Содержание AT90PWM2

Страница 344: ...346 4317I AVR 01 08 AT90PWM2 3 2B 3B 31 1 SO24...

Страница 345: ...347 4317I AVR 01 08 AT90PWM2 3 2B 3B 31 2 SO32...

Страница 346: ...348 4317I AVR 01 08 AT90PWM2 3 2B 3B 31 3 QFN32...

Страница 347: ...349 4317I AVR 01 08 AT90PWM2 3 2B 3B...