ADV8003 Hardware Manual

Rev. B, August 2013

286

Function

bksv_flag_int

Description

0

Interrupt not active

1

Interrupt active. The KSVs from the downstream sink have been read and available in the

Memory Map

hdcp_desired

, TX2 Main Map,

Address 0xF4AF[7]

This bit is used to request HDCP encryption.

Function

hdcp_desired

Description

0

Input audio and video content not to be encrypted

1

Input audio and video content should be encrypted

frame_encryption_en

, TX2 Main Map,

Address 0xF4AF[4]

This bit is used to request HDCP frame encryption.

Function

frame_encryption_en

Description

0

Current video frame should not be encrypted

1

Current video frame should be encrypted

bksv[39:32]

, TX2 Main Map,

Address 0xF4C3[7:0] (Read Only)

This register is used to readback the BKSV Byte 4 read from the downstream Rx by the HDCP controller.

enc_on

, TX2 Main Map,

Address 0xF4B8[6] (Read Only)

This bit is used to readback the HDCP encryption status.

Function

enc_on

Description

0

Audio and video content not being encrypted

1

Audio and video content being encrypted

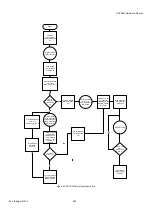

6.13.2.

Multiple Sinks and No Upstream Devices

When connecting the ADV8003 as a source to an HDMI input of a repeater, it is necessary to read all BKSVs from downstream devices.

These BKSVs must be checked against a revocation list, which will be provided on the source content.

will read 0 when the first BKSV interrupt occurs with

set to 1. After the first BKSV interrupt is cleared, if

the sink connected to the ADV8003 is a repeater, a second BKSV interrupt will occur. The ADV8003 will automatically read up to 13 5-

byte BKSVs at a time and store these in the EDID memory. These BKSVs can be accessed from the EDID Map, as shown in

. The

number of additional BKSVs available stored in the EDID Map can be obtained from

. If there are more than 13

additional BKSVs to be processed, the ADV8003 will collect the next up to 13 BKSVs from the sink, then generate another BKSV

interrupt with

set to 1 when the next set is ready.

Содержание ADV8003

Страница 364: ...ADV8003 Hardware Manual Rev B August 2013 364 s HPD HEAC CL DA C_GND 5V G_DET Figure 142 ADV8003 Schematic Page 2...

Страница 365: ...ADV8003 Hardware Manual Rev B August 2013 365 Figure 143 ADV8003 Schematic Page 3 Date August 2011 Rev 0...

Страница 366: ...ADV8003 Hardware Manual Rev B August 2013 366 Figure 144 ADV8003 Schematic Page 4...

Страница 367: ...ADV8003 Hardware Manual Rev B August 2013 367 Figure 145 ADV8003 Schematic Page 5...

Страница 368: ...ADV8003 Hardware Manual Rev B August 2013 368 Figure 146 ADV8003 Schematic Page 6...

Страница 369: ...ADV8003 Hardware Manual Rev B August 2013 369 Figure 147 ADV8003 Schematic Page 7...

Страница 370: ...ADV8003 Hardware Manual Rev B August 2013 370 Figure 148 ADV8003 Schematic Page 8 Date August 2011 Rev 0...

Страница 371: ...ADV8003 Hardware Manual Rev B August 2013 371 Figure 149 ADV8003 Schematic Page 9...

Страница 372: ...ADV8003 Hardware Manual Rev B August 2013 372 Figure 150 ADV8003 Schematic Page 10...

Страница 373: ...ADV8003 Hardware Manual Rev B August 2013 373 Figure 151 ADV8003 Schematic Page 11...

Страница 374: ...ADV8003 Hardware Manual Rev B August 2013 374 Figure 152 ADV8003 Schematic Page 12...

Страница 375: ...ADV8003 Hardware Manual Rev B August 2013 375 Figure 153 ADV8003 Schematic Page 13...

Страница 376: ...ADV8003 Hardware Manual Rev B August 2013 376 Figure 154 ADV8003 Schematic Page 14...

Страница 377: ...ADV8003 Hardware Manual Rev B August 2013 377 Figure 155 ADV8003 Schematic Page 15...

Страница 378: ...ADV8003 Hardware Manual Rev B August 2013 378 Figure 156 ADV8003 Schematic Page 16...

Страница 379: ...ADV8003 Hardware Manual Rev B August 2013 379 Figure 157 ADV8003 Schematic Page 17...

Страница 380: ...ADV8003 Hardware Manual Rev B August 2013 380 Figure 158 ADV8003 Schematic Page 18...

Страница 381: ...ADV8003 Hardware Manual Rev B August 2013 381 Figure 159 ADV8003 Schematic Page 19...

Страница 382: ...ADV8003 Hardware Manual Rev B August 2013 382 Figure 160 ADV8003 Schematic Page 20...

Страница 383: ...ADV8003 Hardware Manual Rev B August 2013 383 Figure 161 ADV8003 Schematic Page 21...

Страница 384: ...ADV8003 Hardware Manual Rev B August 2013 384 Figure 162 ADV8003 Schematic Page 22...

Страница 385: ...ADV8003 Hardware Manual Rev B August 2013 385 Figure 163 ADV8003 Schematic Page 23...

Страница 386: ...ADV8003 Hardware Manual Rev B August 2013 386 Figure 164 ADV8003 Schematic Page 24...

Страница 387: ...ADV8003 Hardware Manual Rev B August 2013 387 Figure 165 ADV8003 Schematic Page 25...

Страница 388: ...ADV8003 Hardware Manual Rev B August 2013 388 Figure 166 ADV8003 Schematic Page 26...

Страница 389: ...ADV8003 Hardware Manual Rev B August 2013 389 Figure 167 ADV8003 Schematic Page 27...

Страница 390: ...ADV8003 Hardware Manual Rev B August 2013 390 Figure 168 ADV8003 Schematic Page 28...

Страница 391: ...ADV8003 Hardware Manual Rev B August 2013 391 Figure 169 ADV8003 Schematic Page 29...

Страница 392: ...ADV8003 Hardware Manual Rev B August 2013 392 Figure 170 ADV8003 Schematic Page 30...

Страница 393: ...ADV8003 Hardware Manual Rev B August 2013 393 Figure 171 ADV8003 Schematic Page 31...

Страница 395: ...ADV8003 Hardware Manual Rev B August 2013 395 Figure 173 ADV8003 Layout Page 2...

Страница 396: ...ADV8003 Hardware Manual Rev B August 2013 396 Figure 174 ADV8003 Layout Page 3...

Страница 397: ...ADV8003 Hardware Manual Rev B August 2013 397 Figure 175 ADV8003 Layout Page 4...

Страница 398: ...ADV8003 Hardware Manual Rev B August 2013 398 Figure 176 ADV8003 Layout Page 5...

Страница 399: ...ADV8003 Hardware Manual Rev B August 2013 399 Figure 177 ADV8003 Layout Page 6...

Страница 400: ...ADV8003 Hardware Manual Rev B August 2013 400 Figure 178 ADV8003 Layout Page 7...

Страница 401: ...ADV8003 Hardware Manual Rev B August 2013 401 Figure 179 ADV8003 Layout Page 8...

Страница 402: ...ADV8003 Hardware Manual Rev B August 2013 402 APPENDIX D PACKAGE OUTLINE DRAWING Refer to Section 1 4...

Страница 427: ...ADV8003 Hardware Manual Rev B August 2013 427 P 2 Z Z Z P 1 Z Z Z P 0 Z Z Z...