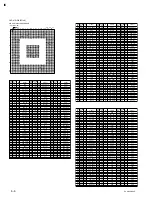

PCS-G50/G50P

6-10

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

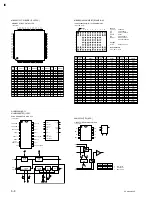

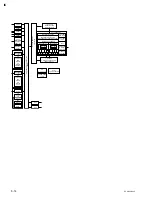

NOISE REDUCTION FOR VIDEO SIGNAL

—TOP VIEW—

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

—

—

I/O

I

I

I

I

I

I

I

I

I

I

I

—

I

—

I

I

I

I

I

I

I

I

NC

GND

SDA

SCL

SLA1

SLA2

YI7

YI6

YI5

YI4

YI3

YI2

YI1

YI0

V

CC

ICLK

GND

CI7

CI6

CI5

CI4

CI3

CI2

CI1

CI0

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

—

—

—

I

I

I

I

—

I

I/O

—

—

—

—

—

—

—

—

—

O

O

O

—

—

—

V

CC

NC

GND

IVS

IHS

MODE0

MODE1

NC

MODE2

CLKO

V

CC

GND

NC

NC

V

CC

NC

NC

NC

NC

OHS

OVS

HREF

GND

NC

V

CC

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

I/O

I/O

I/O

I/O

—

I/O

I/O

I/O

I/O

—

—

—

O

O

O

O

—

O

O

O

O

—

I

I

I

CO0

CO1

CO2

CO3

GND

CO4

CO5

CO6

CO7

V

CC

NC

GND

YO0

YO1

YO2

YO3

V

CC

YO4

YO5

YO6

YO7

GND

TEST7

TEST6

RESET

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

—

—

—

—

—

—

—

—

—

—

—

I

—

I

I

I

I

—

—

—

I

I

—

—

—

V

CC

NC

GND

NC

NC

NC

NC

NC

NC

NC

NC

TEST5

V

CC

TEST4

TEST3

TEST2

TEST1

NC

NC

NC

TESTM

SELF

GND

NC

V

CC

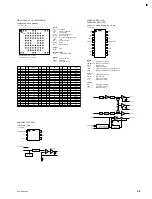

PIN

NO.

I/O

SIGNAL

PIN

NO.

I/O

SIGNAL

PIN

NO.

I/O

SIGNAL

PIN

NO.

I/O

SIGNAL

INPUTS

SCL

SLA1, SLA2

YI0 - YI7

ICLK

CI0 - CI7

IVS

IHS

MODE0 - MODE2

TEST1 - TEST7

RESET

TESTM

SELF

OUTPUTS

OHS

OVS

HREF

YO0 - YO7

INPUTS/OUTPUTS

SDA

CLKO

CO0 - CO7

: I2C BUS CLOCK

: SUB ADDRESS SELECT

: LUMINANCE SIGNAL

: CLOCK

: CHROMINANCE SIGNAL

: VERTICAL SYNC

: HORIZONTAL SYNC

: MODE SELECT

: TEST

: SYSTEM RESET

: MEMORY TEST

: SELF REFRESH SELECT

: HORIZONTAL SYNC

: VERTICAL SYNC

: HORIZONTAL REFERENCE

: LUMINANCE SIGNAL

: I2C BUS DATA

: CLOCK

: CHROMINANCE SIGNAL

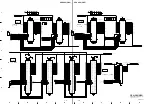

INPUT/OUTPUT

PROCESS

BLOCK

+

3D NR

I2C-BUS

I/F

REGISTER

FRAME

MEMORY

5.6M-BIT

MEMORY

CONTROLLER

ICLK

16

YO0 - YO7

63 - 66, 68 -71

CO0 - CO7

51 - 54, 56 - 59

OHS

45

OVS

46

HREF

47

CLKO

35

IVS

29

IHS

30

SDA

3

YI0 - YI7

14 - 7

CI0 - CI7

25 - 18

4

SCL

75

SLA1, SLA2

5, 6

MODE0 - MODE2

31, 32, 34

RESET

CONTROL SIGNAL

8

8

16

8

8

16

ML87V2105TBZ03A (OKI)

IC

Summary of Contents for Ipels PCS-G50

Page 6: ......

Page 16: ......

Page 26: ......

Page 34: ......

Page 170: ......

Page 186: ......

Page 191: ...PCS G50 G50P 8 7 8 7 CPU 382 B SIDE SUFFIX 12 13 A B C D 1 2 3 4 CPU 382 CPU 382 ...

Page 198: ......

Page 199: ......

Page 200: ...Printed in Japan Sony Corporation 2005 6 22 2005 PCS G50 UC PCS G50P CE E 9 968 181 01 ...