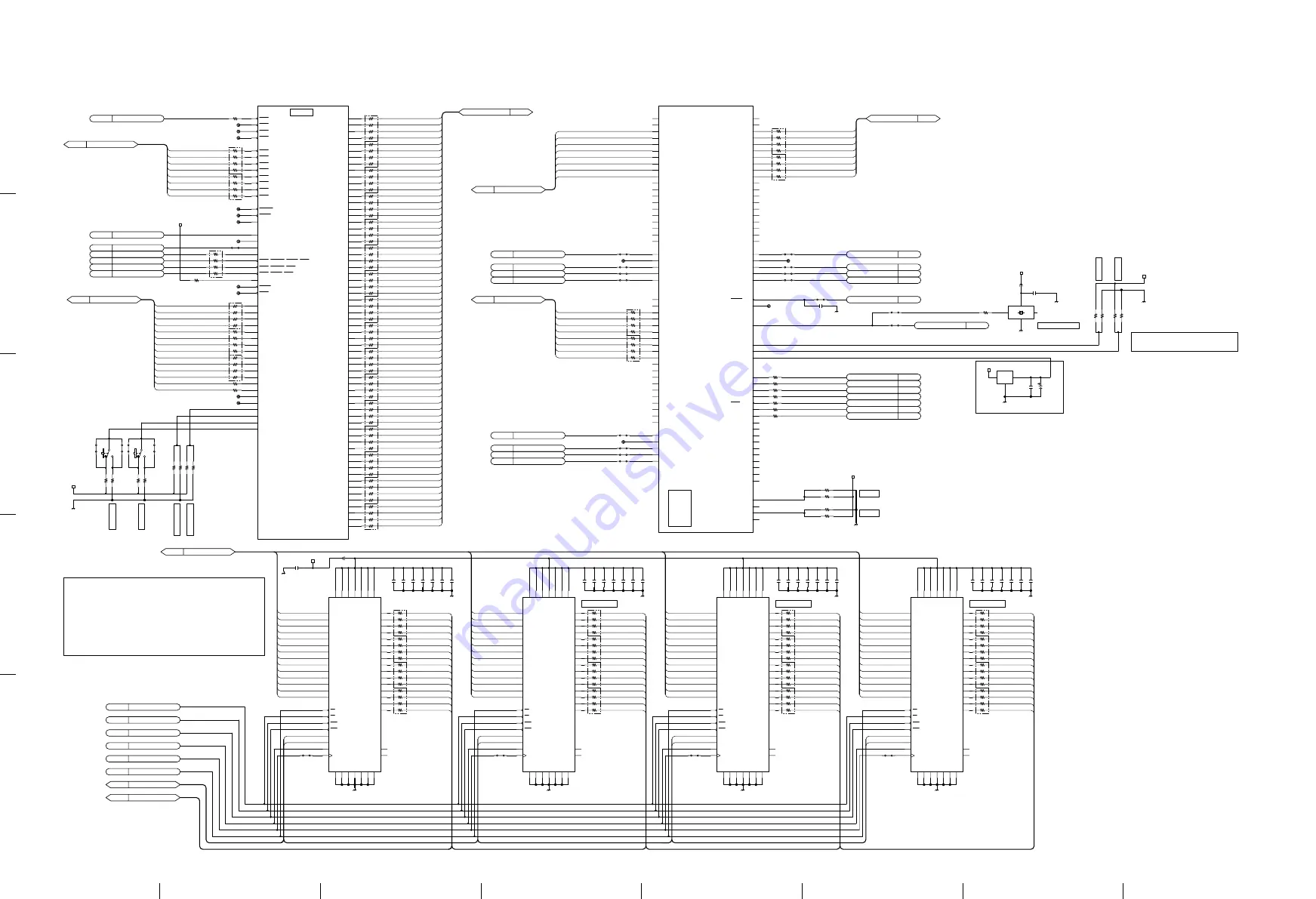

PCS-G50/G50P

7-36

7-36

2

3

4

5

A

B

C

D

E

F

G

H

1

1k

R605

NM

0.1uF

C601

0.1uF

C608

xTDEC_RST

TDEC_EMIFA_AEA(16..3)

006

VFPTDEC_HSYNC

0.1uF

C602

CL614

1.0

D_GND

1k

R625

NM

CL611 1.0

10

R615

EMI

FL601

1

IN

2

OUT

3

GND

TDECVFP_S_YUV(7..0)

013

TMS320DM642GDK6E3

(3/5)

IC501

VP0D_0[AF18]

43

VP0D_1[AE18]

140

VP0D_9[AD15]

226

VP0D_10[AC15]

307

VP0D_11[AB15]

380

VP0D_12/ACLKR0[AD14]

225

VP0D_13/AFSR0[AC14]

306

VP0D_14/AHCLKR0[AB14]

379

VP0D_15/AMUTEIN0[AD13]

224

VP0D_16/AMUTE0[AC13]

305

VP0D_17/ACLKX0[AB13]

378

VP0D_18/AFSX0[AD12]

223

VP0D_19/AHCLKX0[AC12]

304

VP0CLK0[AF14]

39

VP0CLK1[AF12]

37

VP0CTL0[AE17]

139

VP0CTL1[AC17]

309

VP0CTL2[AD17]

228

VP1D_0[AF5]

30

VP1D_1[AF6]

31

VP1D_9[AC8]

300

VP1D_10[AE9]

131

VP1D_11[AD9]

220

VP1D_12/AXR0_0[AC9]

301

VP1D_13/AXR0_1[AD10]

221

VP1D_14/AXR0_2[AC10]

302

VP1D_15/AXR0_3[AE11]

133

VP1D_16/AXR0_4[AD11]

222

VP1D_17/AXR0_5[AC11]

303

VP1D_18/AXR0_6[AB11]

376

VP1D_19/AXR0_7[AB12]

377

VP1CLK0[AF8]

33

VP1CLK1[AF10]

35

VP1CTL0[AF4]

29

VP1CTL1[AE5]

127

VP1CTL2[AD5]

216

VP2D_0[C8]

272

VP2D_1[D8]

349

VP2D_2[A9]

93

VP2D_3[B9]

186

VP2D_4[C9]

271

VP2D_5[D9]

348

VP2D_6[A10]

92

VP2D_7[B10]

185

VP2D_8[C10]

270

VP2D_9[D10]

347

VP2D_10[A11]

91

VP2D_11[B11]

184

VP2D_12[C11]

269

VP2D_13[D11]

346

VP2D_14[E11]

415

VP2D_15[B12]

183

VP2D_16[C12]

268

VP2D_17[D12]

345

VP2D_18[E12]

414

VP2D_19[E13]

413

VP2CLK0[A7]

95

VP2CLK1[A13]

89

VP2CTL0[B8]

187

VP2CTL1[D7]

350

VP2CTL2[C7]

273

TINP1[A5]

97

TOUT1/LENDIAN[B5]

190

TINP0[A4]

98

TOUT0/MAC_EN[C5]

275

EMU11[D17]

340

EMU10[C17]

263

EMU9[B17]

178

EMU8[D16]

341

EMU7[A17]

85

EMU6[C16]

264

EMU5[B16]

179

EMU4[D15]

342

EMU3[C15]

265

EMU2[B15]

180

EMU1[C14]

266

EMU0[A15]

87

TRST[D14]

343

TCK[A16]

86

TDI[A18]

84

TDO[B18]

177

TMS[E15]

411

PLLV[V6]

433

CLKMODE1[AE4]

126

CLKMODE0[AA2]

120

CLKIN[AC2]

122

NMI[B4]

191

RESET[P4]

287

VP0D_3/FSX0[AF16]

41

VP0D_7/FSR0[AB16]

381

VP0D_4/DX0[AE16]

138

VP0D_6/DR0[AC16]

308

VP0D_2/CLKX0[AF17]

42

VP0D_8/CLKR0[AE15]

137

VP0D_5/CLKS0[AD16]

227

VP1D_3/FSX1[AD6]

217

VP1D_7/FSR1[AC7]

299

VP1D_4/DX1[AC6]

298

VP1D_6/DR1[AD7]

218

VP1D_2/CLKX1[AE6]

128

VP1D_8/CLKR1[AD8]

219

VP1D_5/CLKS1[AE7]

129

TDEC_EMIFA_AED(63..0) 006

R621

1k NM

1k

R628

NM

CL609 1.0

0.1uF

C627

0.1uF

C628

1k

R626

0.1uF

C604

0.1uF

C629

1k

R606

22

R611

CNTI2F_JT_TCK

003,004,009

0.1uF

C624

10

RB608

1

2

3

4

5

6

7

8

VFPTDEC_FIELD

D_GND

VFPTDEC_HSYNC

22

R610

TDEC_CLK

002

D_GND

TMS320DM642GDK6E3

(2/5)

IC501

ACE0[K25]

162

ACE1[K24]

249

ACE2[K23]

328

ACE3[L26]

66

ABE0[L24]

248

ABE1[L23]

327

ABE2[M26]

65

ABE3[M25]

160

ABE4[R26]

62

ABE5[R25]

157

ABE6[T23]

322

ABE7[T22]

393

AHOLDA[N22]

396

AHOLD[W24]

240

ABUSREQ[P22]

395

AECLKIN[H25]

164

AECLKOUT2[J23]

329

AECLKOUT1[J26]

68

ASDCKE[L25]

161

AARE/ASDCAS/ASADS/ASRE[J25]

163

AAOE/ASDRAS/ASOE[J24]

250

AAWE/ASDWE/ASWE[K26]

67

AARDY[L22]

398

ASOE3[R22]

394

APDT[M22]

397

AEA3[M24]

247

AEA4[M23]

326

AEA5[N26]

64

AEA6[N24]

246

AEA7[N23]

325

AEA8[P26]

63

AEA9[P24]

245

AEA10[P23]

324

AEA11[R24]

244

AEA12[R23]

323

AEA13[T25]

156

AEA14[T24]

243

AEA15[U26]

60

AEA16[U25]

155

AEA17[U24]

242

AEA18[V23]

320

AEA19[V26]

59

AEA20[V25]

154

AEA21[V24]

241

AEA22[U23]

321

AED63[AF24]

49

AED62[AF23]

48

AED61[AE23]

145

AED60[AD23]

234

AED59[AD22]

233

AED58[AE22]

144

AED57[AD21]

232

AED56[AE21]

143

AED55[AC21]

313

AED54[AF21]

46

AED53[AD20]

231

AED52[AE20]

142

AED51[AC20]

312

AED50[AF20]

45

AED49[AC19]

311

AED48[AD19]

230

AED47[W23]

319

AED46[Y26]

57

AED45[Y23]

318

AED44[Y25]

152

AED43[Y24]

239

AED42[AA26]

56

AED41[AA23]

317

AED40[AA25]

151

AED39[AA24]

238

AED38[AB23]

316

AED37[AB25]

150

AED36[AB24]

237

AED35[AC26]

54

AED34[AC25]

149

AED33[AD25]

148

AED32[AD26]

53

AED31[C26]

74

AED30[C25]

169

AED29[D26]

73

AED28[D25]

168

AED27[E24]

254

AED26[E25]

167

AED25[F24]

253

AED24[F25]

166

AED23[F23]

332

AED22[F26]

71

AED21[G24]

252

AED20[G25]

165

AED19[G23]

331

AED18[G26]

70

AED17[H23]

330

AED16[H24]

251

AED15[C19]

261

AED14[D19]

338

AED13[A20]

82

AED12[D20]

337

AED11[B20]

175

AED10[C20]

260

AED9[A21]

81

AED8[D21]

336

AED7[B21]

174

AED6[C21]

259

AED5[A23]

79

AED4[C22]

258

AED3[B22]

173

AED2[B23]

172

AED1[A24]

78

AED0[B24]

171

0

JC605

0

JC613

D_GND

VFPTDEC_VSYNC

10

RB610

1

2

3

4

5

6

7

8

TDEC_EMIFA_AECLKIN

005

0

JC601

NM

CL604 1.0

0.1uF

C606

0

JC608

0.1uF

C614

D_GND

CL613

1.0

TDEC_EMIFA_xACE0

006

10

RB622

1

2

3

4

5

6

7

8

TDEC_EMIFA_AECLKOUT1

TDEC_EMIFA_xABE(7..0)

TDEC_EMIFA_xASDCAS

22

RB640

1

2

3

4

5

6

7

8

0.1uF

C620

0

JC616

10

R614

D_GND

CL601 1.0

S601

NM

1

2

3

0

JC606

22

RB633

1

2

3

4

5

6

7

8

0.1uF

C611

22

R612

CL605 1.0

MT48LC8M16A2P-75-Y15WTR

IC603

VDD1

1

DQ0

2

VDDQ1

3

DQ1

4

DQ2

5

VSSQ1

6

DQ3

7

DQ4

8

VDDQ2

9

DQ5

10

DQ6

11

VSSQ2

12

DQ7

13

VDD2

14

DQML

15

WE

16

CAS

17

RAS

18

CS

19

BA0

20

BA1

21

A10

22

A0

23

A1

24

A2

25

A3

26

VDD3

27

VSS3

54

DQ15

53

VSSQ4

52

DQ14

51

DQ13

50

VDDQ4

49

DQ12

48

DQ11

47

VSSQ3

46

DQ10

45

DQ9

44

VDDQ3

43

DQ8

42

VSS2

41

NC2

40

DQMH

39

CLK

38

CKE

37

NC1

36

A11

35

A9

34

A8

33

A7

32

A6

31

A5

30

A4

29

VSS1

28

1k

R609

TDEC_EMIFA_AED(63..0)

0.1uF

C613

CL612

1.0

10

RB617

1

2

3

4

5

6

7

8

0.1uF

C605

R622

1k NM

0.1uF

C625

D_GND

0.1uF

C610

22

RB630

1

2

3

4

5

6

7

8

MT48LC8M16A2P-75-Y15WTR

IC602

VDD1

1

DQ0

2

VDDQ1

3

DQ1

4

DQ2

5

VSSQ1

6

DQ3

7

DQ4

8

VDDQ2

9

DQ5

10

DQ6

11

VSSQ2

12

DQ7

13

VDD2

14

DQML

15

WE

16

CAS

17

RAS

18

CS

19

BA0

20

BA1

21

A10

22

A0

23

A1

24

A2

25

A3

26

VDD3

27

VSS3

54

DQ15

53

VSSQ4

52

DQ14

51

DQ13

50

VDDQ4

49

DQ12

48

DQ11

47

VSSQ3

46

DQ10

45

DQ9

44

VDDQ3

43

DQ8

42

VSS2

41

NC2

40

DQMH

39

CLK

38

CKE

37

NC1

36

A11

35

A9

34

A8

33

A7

32

A6

31

A5

30

A4

29

VSS1

28

0

JC612

22

RB605

1

2

3

4

5

6

7

8

10

RB615

1

2

3

4

5

6

7

8

10

R613

10

RB618

1

2

3

4

5

6

7

8

10

RB612

1

2

3

4

5

6

7

8

10

RB607

1

2

3

4

5

6

7

8

22

RB635

1

2

3

4

5

6

7

8

TDEC_EMIFA_xABE(7..0)

006

0

JC611

TDEC_EMIFA_xASDRAS

006

VFPTDEC_VSYNC

D2S_3.3V

TDEC_EMIFA_AECLKOUT1

006

FB601

27M_TDEC

TDEC_EMIFA_xACE0

10

R619

0.1uF

C607

TDEC_EMIFA_xASDRAS

0.1uF

C631

CNTI2F_JT_TMS

003,004,009

0.1uF

C615

10

R617

0

JC618

MT48LC8M16A2P-75-Y15WTR

IC604

VDD1

1

DQ0

2

VDDQ1

3

DQ1

4

DQ2

5

VSSQ1

6

DQ3

7

DQ4

8

VDDQ2

9

DQ5

10

DQ6

11

VSSQ2

12

DQ7

13

VDD2

14

DQML

15

WE

16

CAS

17

RAS

18

CS

19

BA0

20

BA1

21

A10

22

A0

23

A1

24

A2

25

A3

26

VDD3

27

VSS3

54

DQ15

53

VSSQ4

52

DQ14

51

DQ13

50

VDDQ4

49

DQ12

48

DQ11

47

VSSQ3

46

DQ10

45

DQ9

44

VDDQ3

43

DQ8

42

VSS2

41

NC2

40

DQMH

39

CLK

38

CKE

37

NC1

36

A11

35

A9

34

A8

33

A7

32

A6

31

A5

30

A4

29

VSS1

28

10

RB616

1

2

3

4

5

6

7

8

R620

1k

1k

R603

0

JC621

TENCTDEC_JT_DATA

003

R623

1k

TDEC_EMIFA_xASDCAS

006

0

JC607

0.1uF

C617

S602

NM

1

2

3

22

RB604

1

2

3

4

5

6

7

8

VFPTDEC_VSYNC

D_GND

22

RB636

1

2

3

4

5

6

7

8

TDEC_EMIFA_AEA(16..3)

006

TDECTMUX_JT_DATA

009

D_GND

1k

R602

CL608 1.0

D2S_3.3V

0

JC614

10

RB609

1

2

3

4

5

6

7

8

VFPTDEC_FIELD

0.1uF

C630

CNTI2F_JT_TRST

003,004,009

0.001uF

C623

VFPTDEC_FIELD

0.1uF

C619

D2S_3.3V

1k

R627

0.1uF

C621

27M_TDEC

0

JC620

10

RB621

1

2

3

4

5

6

7

8

CL606 1.0

VFPTDEC_HSYNC

D2S_3.3V

22

RB627

1

2

3

4

5

6

7

8

10

R618

10

RB614

1

2

3

4

5

6

7

8

D_GND

D_GND

0.1uF

C622

1k

R607

NM

CL615

1.0

22

RB629

1

2

3

4

5

6

7

8

CL603 1.0

22

RB628

1

2

3

4

5

6

7

8

16V

10uF

C633

CL610 1.0

D_GND

D_GND

0

JC609

1k

R604

TDEC_EMIFA_xASDWE

006

CL602 1.0

TDEC_EMIFA_xASDWE

10

RB620

1

2

3

4

5

6

7

8

TDECVFP_M_YUV(7..0)

013

TDEC_EMIFA_ASDCKE

22

RB606

1

2

3

4

5

6

7

8

0

JC603

10k

R608

NM

22

RB601

1

2

3

4

5

6

7

8

22

RB639

1

2

3

4

5

6

7

8

0.1uF

C618

10

RB619

1

2

3

4

5

6

7

8

10

RB611

1

2

3

4

5

6

7

8

0

JC604

NM

D_GND

22

RB642

1

2

3

4

5

6

7

8

0.1uF

C626

10

RB613

1

2

3

4

5

6

7

8

0

JC617

CL607 1.0

0

JC610

D2S_3.3V

1k

R601

0.1uF

C603

22

RB602

1

2

3

4

5

6

7

8

TDEC_EMIFA_ASDCKE

006

22

RB624

1

2

3

4

5

6

7

8

0.1uF

C612

0

JC602

0.1uF

C609

0

JC622

22

RB623

1

2

3

4

5

6

7

8

22

RB634

1

2

3

4

5

6

7

8

22

RB625

1

2

3

4

5

6

7

8

0.1uF

C616

22

RB626

1

2

3

4

5

6

7

8

22

RB603

1

2

3

4

5

6

7

8

0

JC619

MT48LC8M16A2P-75-Y15WTR

IC601

VDD1

1

DQ0

2

VDDQ1

3

DQ1

4

DQ2

5

VSSQ1

6

DQ3

7

DQ4

8

VDDQ2

9

DQ5

10

DQ6

11

VSSQ2

12

DQ7

13

VDD2

14

DQML

15

WE

16

CAS

17

RAS

18

CS

19

BA0

20

BA1

21

A10

22

A0

23

A1

24

A2

25

A3

26

VDD3

27

VSS3

54

DQ15

53

VSSQ4

52

DQ14

51

DQ13

50

VDDQ4

49

DQ12

48

DQ11

47

VSSQ3

46

DQ10

45

DQ9

44

VDDQ3

43

DQ8

42

VSS2

41

NC2

40

DQMH

39

CLK

38

CKE

37

NC1

36

A11

35

A9

34

A8

33

A7

32

A6

31

A5

30

A4

29

VSS1

28

D2S_3.3V

27M_TDEC

VFPTDEC_YUV(7..0)

013

0

JC615

22

RB641

1

2

3

4

5

6

7

8

TI2FCN_JT_EMU1

003,004,009

TI2FCN_JT_EMU0

003,004,009

47

RB632

1

2

3

4

5

6

7

8

47

RB631

1

2

3

4

5

6

7

8

47

RB637

1

2

3

4

5

6

7

8

47

RB638

1

2

3

4

5

6

7

8

FB602

NM

0

JC623

NM

D_GND

50MHz

X601

NM

1

CONT

2

Vss

3

OUT

4

Vdd

D_GND

22

R624

NM

0.1uF

C632

NM

0

JC624

10

R616

D2S_3.3V

TDEC_EMIFA_xABE1

TDEC_EMIFA_xABE0

TDEC_EMIFA_xABE4

TDEC_EMIFA_xABE7

TDEC_EMIFA_xABE6

TDEC_EMIFA_xABE5

TDEC_EMIFA_xABE2

TDEC_EMIFA_xABE3

TDEC_EMIFA_xABE0

TDEC_EMIFA_xABE1

TDEC_EMIFA_xABE2

TDEC_EMIFA_xABE3

TDEC_EMIFA_xABE4

TDEC_EMIFA_xABE5

TDEC_EMIFA_xABE6

TDEC_EMIFA_xABE7

TDEC_EMIFA_AEA3

TDEC_EMIFA_AEA4

TDEC_EMIFA_AEA5

TDEC_EMIFA_AEA6

TDEC_EMIFA_AEA7

TDEC_EMIFA_AEA8

TDEC_EMIFA_AEA9

TDEC_EMIFA_AEA10

TDEC_EMIFA_AEA11

TDEC_EMIFA_AEA12

TDEC_EMIFA_AEA13

TDEC_EMIFA_AEA14

TDEC_EMIFA_AEA15

TDEC_EMIFA_AEA16

TDEC_EMIFA_AED0

TDEC_EMIFA_AED1

TDEC_EMIFA_AED2

TDEC_EMIFA_AED3

TDEC_EMIFA_AED4

TDEC_EMIFA_AED5

TDEC_EMIFA_AED6

TDEC_EMIFA_AED7

TDEC_EMIFA_AED8

TDEC_EMIFA_AED9

TDEC_EMIFA_AED10

TDEC_EMIFA_AED11

TDEC_EMIFA_AED12

TDEC_EMIFA_AED13

TDEC_EMIFA_AED14

TDEC_EMIFA_AED15

TDEC_EMIFA_AED16

TDEC_EMIFA_AED17

TDEC_EMIFA_AED18

TDEC_EMIFA_AED19

TDEC_EMIFA_AED20

TDEC_EMIFA_AED21

TDEC_EMIFA_AED22

TDEC_EMIFA_AED23

TDEC_EMIFA_AED24

TDEC_EMIFA_AED25

TDEC_EMIFA_AED26

TDEC_EMIFA_AED27

TDEC_EMIFA_AED28

TDEC_EMIFA_AED29

TDEC_EMIFA_AED30

TDEC_EMIFA_AED31

TDEC_EMIFA_AED32

TDEC_EMIFA_AED33

TDEC_EMIFA_AED34

TDEC_EMIFA_AED35

TDEC_EMIFA_AED36

TDEC_EMIFA_AED37

TDEC_EMIFA_AED38

TDEC_EMIFA_AED39

TDEC_EMIFA_AED40

TDEC_EMIFA_AED41

TDEC_EMIFA_AED42

TDEC_EMIFA_AED43

TDEC_EMIFA_AED44

TDEC_EMIFA_AED45

TDEC_EMIFA_AED46

TDEC_EMIFA_AED47

TDEC_EMIFA_AED48

TDEC_EMIFA_AED49

TDEC_EMIFA_AED50

TDEC_EMIFA_AED51

TDEC_EMIFA_AED52

TDEC_EMIFA_AED53

TDEC_EMIFA_AED54

TDEC_EMIFA_AED55

TDEC_EMIFA_AED56

TDEC_EMIFA_AED57

TDEC_EMIFA_AED58

TDEC_EMIFA_AED59

TDEC_EMIFA_AED60

TDEC_EMIFA_AED61

TDEC_EMIFA_AED62

TDEC_EMIFA_AED63

VFPTDEC_YUV0

VFPTDEC_YUV1

VFPTDEC_YUV2

VFPTDEC_YUV3

VFPTDEC_YUV4

VFPTDEC_YUV5

VFPTDEC_YUV6

VFPTDEC_YUV7

TDEC_EMIFA_AEA3

TDEC_EMIFA_AEA4

TDEC_EMIFA_AEA5

TDEC_EMIFA_AEA6

TDEC_EMIFA_AEA7

TDEC_EMIFA_AEA8

TDEC_EMIFA_AEA9

TDEC_EMIFA_AEA10

TDEC_EMIFA_AEA11

TDEC_EMIFA_AEA12

TDEC_EMIFA_AEA13

TDEC_EMIFA_AEA14

TDEC_EMIFA_AEA15

TDEC_EMIFA_AEA16

TDEC_EMIFA_AED0

TDEC_EMIFA_AED1

TDEC_EMIFA_AED2

TDEC_EMIFA_AED3

TDEC_EMIFA_AED4

TDEC_EMIFA_AED5

TDEC_EMIFA_AED6

TDEC_EMIFA_AED7

TDEC_EMIFA_AED8

TDEC_EMIFA_AED9

TDEC_EMIFA_AED10

TDEC_EMIFA_AED11

TDEC_EMIFA_AED12

TDEC_EMIFA_AED13

TDEC_EMIFA_AED14

TDEC_EMIFA_AED15

TDEC_EMIFA_AED16

TDEC_EMIFA_AED17

TDEC_EMIFA_AED18

TDEC_EMIFA_AED19

TDEC_EMIFA_AED20

TDEC_EMIFA_AED21

TDEC_EMIFA_AED22

TDEC_EMIFA_AED23

TDEC_EMIFA_AED24

TDEC_EMIFA_AED25

TDEC_EMIFA_AED26

TDEC_EMIFA_AED27

TDEC_EMIFA_AED28

TDEC_EMIFA_AED29

TDEC_EMIFA_AED30

TDEC_EMIFA_AED31

TDEC_EMIFA_AED32

TDEC_EMIFA_AED33

TDEC_EMIFA_AED34

TDEC_EMIFA_AED35

TDEC_EMIFA_AED36

TDEC_EMIFA_AED37

TDEC_EMIFA_AED38

TDEC_EMIFA_AED39

TDEC_EMIFA_AED40

TDEC_EMIFA_AED41

TDEC_EMIFA_AED42

TDEC_EMIFA_AED43

TDEC_EMIFA_AED44

TDEC_EMIFA_AED45

TDEC_EMIFA_AED46

TDEC_EMIFA_AED47

TDEC_EMIFA_AED48

TDEC_EMIFA_AED49

TDEC_EMIFA_AED50

TDEC_EMIFA_AED51

TDEC_EMIFA_AED52

TDEC_EMIFA_AED53

TDEC_EMIFA_AED54

TDEC_EMIFA_AED55

TDEC_EMIFA_AED56

TDEC_EMIFA_AED57

TDEC_EMIFA_AED58

TDEC_EMIFA_AED59

TDEC_EMIFA_AED60

TDEC_EMIFA_AED61

TDEC_EMIFA_AED62

TDEC_EMIFA_AED63

TDEC_EMIFA_AEA4

TDEC_EMIFA_AEA6

TDEC_EMIFA_AEA8

TDEC_EMIFA_AEA5

TDEC_EMIFA_AEA9

TDEC_EMIFA_AEA3

TDEC_EMIFA_AEA16

TDEC_EMIFA_AEA10

TDEC_EMIFA_AEA12

TDEC_EMIFA_AEA14

TDEC_EMIFA_AEA13

TDEC_EMIFA_AEA15

TDEC_EMIFA_AEA11

TDEC_EMIFA_AEA7

TDEC_EMIFA_AEA4

TDEC_EMIFA_AEA6

TDEC_EMIFA_AEA8

TDEC_EMIFA_AEA5

TDEC_EMIFA_AEA9

TDEC_EMIFA_AEA3

TDEC_EMIFA_AEA16

TDEC_EMIFA_AEA10

TDEC_EMIFA_AEA12

TDEC_EMIFA_AEA14

TDEC_EMIFA_AEA13

TDEC_EMIFA_AEA15

TDEC_EMIFA_AEA11

TDEC_EMIFA_AEA7

TDEC_EMIFA_AEA4

TDEC_EMIFA_AEA6

TDEC_EMIFA_AEA8

TDEC_EMIFA_AEA5

TDEC_EMIFA_AEA9

TDEC_EMIFA_AEA3

TDEC_EMIFA_AEA16

TDEC_EMIFA_AEA10

TDEC_EMIFA_AEA12

TDEC_EMIFA_AEA14

TDEC_EMIFA_AEA13

TDEC_EMIFA_AEA15

TDEC_EMIFA_AEA11

TDEC_EMIFA_AEA7

TDECVFP_M_YUV0

TDECVFP_M_YUV1

TDECVFP_M_YUV2

TDECVFP_M_YUV3

TDECVFP_M_YUV4

TDECVFP_M_YUV5

TDECVFP_M_YUV6

TDECVFP_M_YUV7

TDECVFP_S_YUV0

TDECVFP_S_YUV1

TDECVFP_S_YUV2

TDECVFP_S_YUV3

TDECVFP_S_YUV4

TDECVFP_S_YUV5

TDECVFP_S_YUV6

TDECVFP_S_YUV7

MAC_EN

Endian

11 - Reserved

BootMode1

AEA[20:19]:Clock mode select for EMIFA (AECLKIN_SEL[1:0])

BootMode0

8M*16bit,16MB

01 - CPU/4 Clock Rate

EMIFA

TI-DSP-DEC(3/5)

11 - EMIFA boot

CLOCK

JTAG

AECLKIN_SEL0

CLKMODE[1:0]:Clock mode select

TI-DSP-DEC(2/5)

8M*16bit,16MB

8M*16bit,16MB

RESET

01 - HPI boot

00 - Bypassx1

00 - AECLKIN (default mode)

8M*16bit,16MB

10 - CPU/6 Clock Rate

TIMER

AEA[22:21]:Boot mode

AECLKIN_SEL1

10 - x12

01 - x6

11 - Reserved

McBSP

10 - Reserved

00 - No boot

CLKMODE1

CLKMODE0

TDEC CLKIN

001,002

006,013

006,013

006,013

001,006

006,013

001,006

006,013

006,013

006,013

006,013

001,006

006,013

006

006

006

006

006

006

006

006

DSP-113 (6/20)

DSP-113 (6/20)

DSP-113 (6/20)

BOARD NO. 1-864-975-12

NMX-192_DSP-113_014_6

Summary of Contents for Ipels PCS-G50

Page 6: ......

Page 16: ......

Page 26: ......

Page 34: ......

Page 170: ......

Page 186: ......

Page 191: ...PCS G50 G50P 8 7 8 7 CPU 382 B SIDE SUFFIX 12 13 A B C D 1 2 3 4 CPU 382 CPU 382 ...

Page 198: ......

Page 199: ......

Page 200: ...Printed in Japan Sony Corporation 2005 6 22 2005 PCS G50 UC PCS G50P CE E 9 968 181 01 ...