connections with the system timing slot module. This allows peripheral modules to send

triggers to the system timing module using PXIe_DSTARC and for the system timing module

to send triggers to peripheral modules using PXIe_DSTARB. Both PXIe_DSTARB and

PXIe_DSTARC are one directional. The PXI Express Specification requires PXI Express

chassis to limit the skew between any two PXIe_DSTAR routes to 150 ps.

The PXIe-6674T receives PXIe_DSTARC and can route it to both the PXIe_DSTARA

network for use as a clock source and to the FPGA for use as a trigger source. The

PXIe-6674T can independently select from the following sources to be routed to

PXIe_DSTARB:

•

PFI<0..5>

•

PFI_LVDS<0..2>

•

PXI Triggers<0..7> (PXI_TRIG<0..7>)

•

PXI Star Triggers (PXI_STAR<0..16>)

•

PXIe_DSTARC<0..16>

•

Global Software Trigger

•

Steady logic high or low

•

Backplane synchronization clock

section for more information on the backplane

synchronization clock.

Choosing the Type of Routing

The PXIe-6674T routes signals in one of two ways: asynchronously or synchronously. The

following sections describe the two routing types and the considerations for choosing each

type.

Asynchronous Routing

Asynchronous routing is the most straightforward method of routing signals. Any

asynchronous route can be defined in terms of two signals: a

source

and a

destination

. A

digital pulse or train comes in on the source and is propagated to the destination. When the

source signal goes from low to high, this rising edge is transferred to the destination after a

propagation delay through the module.

on page 27 illustrates an asynchronous

routing operation.

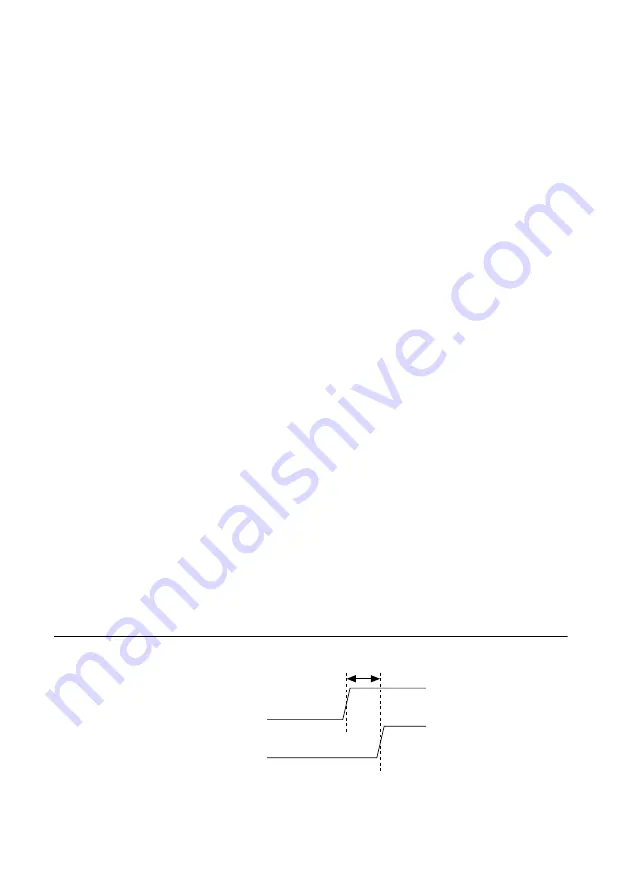

Figure 8. Asynchronous Routing Operation

Trigger Input

Trigger Output

Propagation Delay

t

pd

PXIe-6674T User Manual

|

© National Instruments

|

27