4-6

|

ni.com

Chapter 4

Developing with LabVIEW FPGA

For more information about

Run

,

Reset

, and other Invoke methods, refer to the

LabVIEW FPGA Module Help

.

Note

When self-configuration executes, the clocking configuration enters an

indeterminate state. When the clocking configuration is in an indeterminate state, you

cannot rely on clocking stability from the clocking and routing hardware on the

NI-793xR.

Streaming

Flow Control

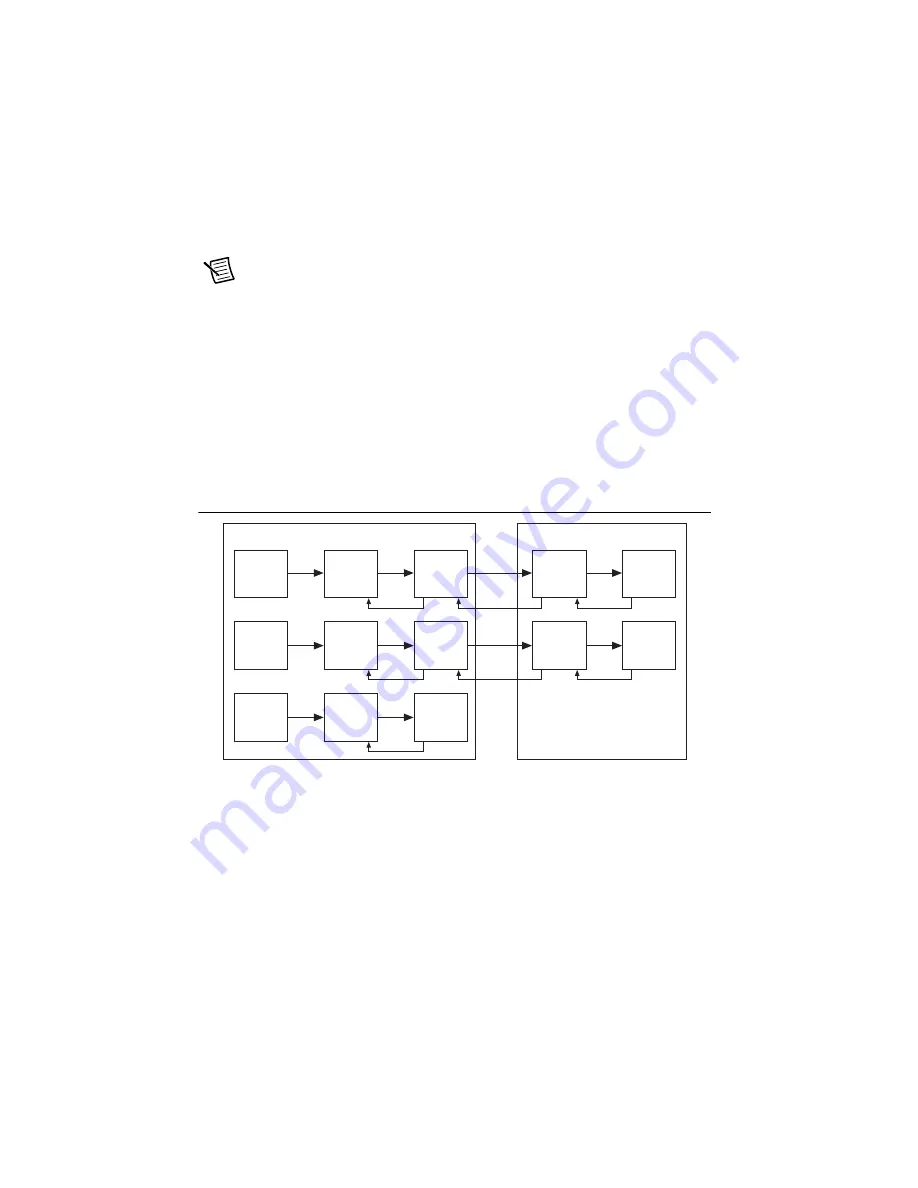

Any application that logs information must have rigorous flow control because the FlexRIO

adapter module can generate far more data than the application nodes can process. The

FPGA-to-Host FIFO uses Ready for Input signals to communicate to the DRAM whether it is

ready to process more data. The following figure demonstrates how you can implement flow

control on an NI-793xR target.

Figure 4-1.

Host-Side FIFO to FPGA Flow Control

For information about data transfer rates, refer to the following sections:

•

•

•

Re

a

dy?

Re

a

dy?

Re

a

dy?

Re

a

dy?

Re

a

dy?

Re

a

dy?

Re

a

dy?

D

a

t

a

DRAM/

BRAM

MGT

D

a

t

a

DRAM/

BRAM

T

a

rget

to Ho

s

t

FIFO

Ho

s

t

S

ide

FIFO

SS

D

D

a

t

a

DRAM/

BRAM

T

a

rget

to

Ho

s

t

Ho

s

t

S

ide

FIFO

NIL

FPGA Mod

u

le

Re

a

l-Time Controller