2.2.1 (2) ADD (W)

ADD (ADD binary)

Add Binary

Operation

Rd + (EAs)

→

Rd

Assembly-Language Format

ADD.W

<EAs>, Rd

Operand Size

Word

Condition Code

H: Set to 1 if there is a carry at bit 11;

otherwise cleared to 0.

N: Set to 1 if the result is negative; otherwise

cleared to 0.

Z:

Set to 1 if the result is zero; otherwise

cleared to 0.

V: Set to 1 if an overflow occurs; otherwise

cleared to 0.

C: Set to 1 if there is a carry at bit 15;

otherwise cleared to 0.

I

UI

H

U

N

Z

V

C

—

—

↕

—

↕

↕

↕

↕

Description

This instruction adds the source operand to the contents of a 16-bit register Rd (destination

operand) and stores the result in the 16-bit register Rd.

Available Registers

Rd:

R0 to R7, E0 to E7

Rs:

R0 to R7, E0 to E7

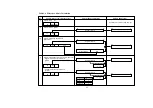

Operand Format and Number of States Required for Execution

Notes

Instruction Format

1st byte

2nd byte

3rd byte

4th byte

Immediate

ADD.W

#xx:16, Rd

7

9

1

rd

IMM

4

Register direct

ADD.W

Rs, Rd

0

9

rs

rd

2

No. of

States

Addressing

Mode

Mnemonic

Operands

43