1.6.2 Instructions and Addressing Modes

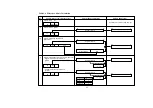

Table 1-2 indicates the instructions available in the H8/300H CPU.

Table 1-2 Instruction Set Overview

16

Addressing Modes

Function

Instruction

#xx

Rn

@ERn

@(d:16,ERn)

@(d:24,ERn)

@ERn+/@–ERn

@aa:8 @aa:16 @aa:24 @(d:8,PC) @(d:16,PC) @@aa:8

—

MOV

POP, PUSH

MOVFPE,

MOVTPE

ADD, CMP

SUB

ADDX,

SUBX

ADDS,

SUBS

INC, DEC

DAA, DAS

MULXU,

DIVXU

MULXS,

DIVXS

NEG

EXTU, EXTS

AND, OR,

XOR

NOT

Data

transfer

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

Arithmetic

operations

Logic

operations

Shift

Bit manipu-

lation

BWL

—

—

BWL

WL

B

—

—

—

—

—

—

—

BWL

—

—

—

BWL

—

—

BWL

BWL

B

L

*

1

BWL

B

BW

BW

BWL

WL

BWL

BWL

BWL

B

BWL

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

B

BWL

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

BWL

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

BWL

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

B

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

B

BWL

—

B

—

—

—

—

—

—

—

—

—

—

—

—

—

—

BWL

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

WL

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—