18

EPSON

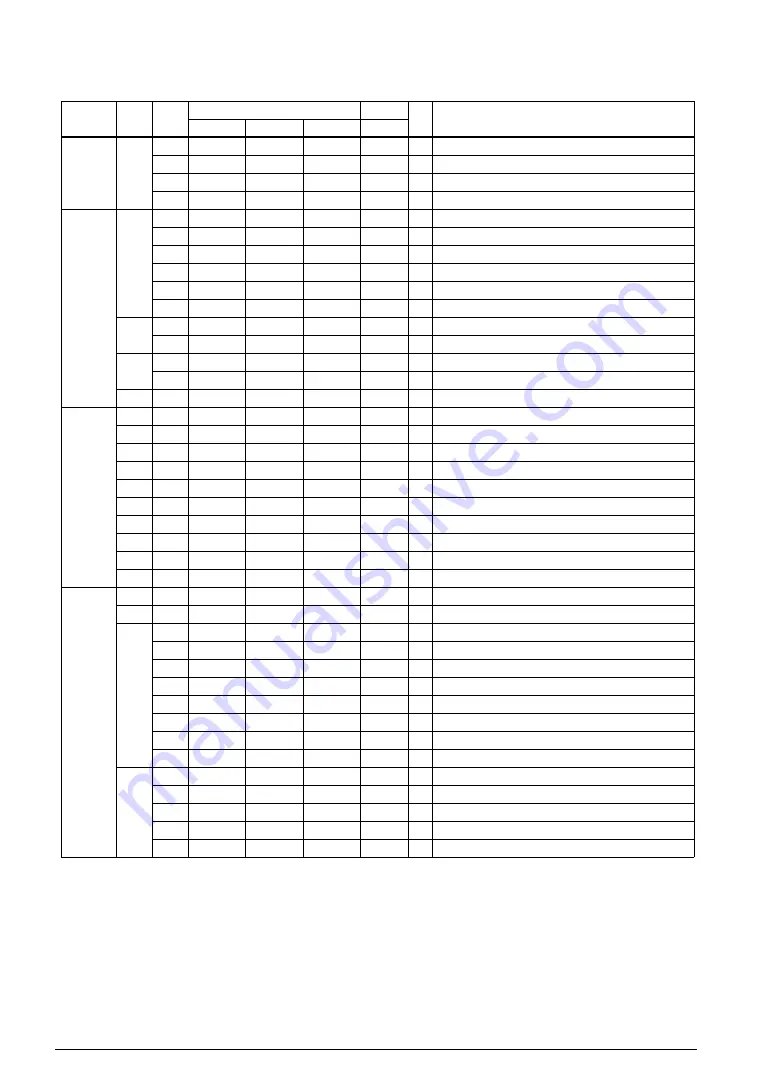

S1C6200/6200A CORE CPU MANUAL

3 INSTRUCTION SET

B

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

A

0

0

0

0

1

1

1

1

1

1

1

1

1

1

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

9

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

8

0

0

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

7

0

0

0

0

0

1

1

1

1

1

0

1

0

1

e7

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

6

1

1

1

1

0

1

0

0

0

0

1

1

1

1

e6

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

5

0

0

1

1

r1

0

1

1

0

0

1

1

1

1

e5

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

4

0

1

0

1

r0

0

0

1

0

1

0

0

1

1

e4

0

1

0

1

0

1

0

1

0

1

1

0

0

0

0

0

0

0

0

0

1

1

1

1

1

3

i3

i3

i3

i3

i3

r1

n3

n3

n3

n3

i3

r1

i3

r1

e3

i3

i3

0

1

0

1

0

1

1

0

1

1

0

0

0

0

0

1

1

1

0

0

0

0

0

2

i2

i2

i2

i2

i2

r0

n2

n2

n2

n2

i2

r0

i2

r0

e2

i2

i2

0

1

0

1

1

0

0

1

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

1

i1

i1

i1

i1

i1

q1

n1

n1

n1

n1

i1

q1

i1

q1

e1

i1

i1

0

1

1

0

0

1

0

1

1

1

r1

0

0

1

1

0

0

1

r1

0

0

1

1

0

i0

i0

i0

i0

i0

q0

n0

n0

n0

n0

i0

q0

i0

q0

e0

i0

i0

1

0

0

1

0

1

0

1

1

1

r0

0

1

0

1

0

1

0

r0

0

1

0

1

XH, i

XL, i

YH, i

YL, i

r, i

r, q

A, Mn

B, Mn

Mn, A

Mn, B

MX, i

r, q

MY, i

r, q

MX, e

F, i

F, i

SP

SP

r

XP

XH

XL

YP

YH

YL

F

r

XP

XH

XL

YP

CP

LD

LDPX

LDPY

LBPX

SET

RST

SCF

RCF

SZF

RZF

SDF

RDF

EI

DI

INC

DEC

PUSH

POP

Index

operation

instructions

Data

transfer

instructions

Flag

operation

instructions

Stack

operation

instructions

Classification

Operand

I D Z C

↑

↓

↑

↓

↑

↑

↑

↑

↑

↓

↑

↓

↑

↑

↑

↑

↑

↓

↑

↓

7

7

7

7

5

5

5

5

5

5

5

5

5

5

5

7

7

7

7

7

7

7

7

7

7

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

Clock

Operation Code

Flag

XH-i3~i0

XL-i3~i0

YH-i3~i0

YL-i3~i0

r

←

i3~i0

r

←

q

A

←

M(n3~n0)

B

←

M(n3~n0)

M(n3~n0)

←

A

M(n3~n0)

←

B

M(X)

←

i3~i0, X

←

X+1

r

←

q, X

←

X+1

M(Y)

←

i3~i0, Y

←

Y+1

r

←

q, Y

←

Y+1

M(X)

←

e3~e0, M(X+1)

←

e7~e4, X

←

X+2

F

←

F

V

i3~i0

F

←

F

Λ

i3~i0

C

←

1

C

←

0

Z

←

1

Z

←

0

D

←

1 (Decimal Adjuster ON)

D

←

0 (Decimal Adjuster OFF)

I

←

1 (Enables Interrupt)

I

←

0 (Disables Interrupt)

SP

←

SP+1

SP

←

SP-1

SP

←

SP-1, M(SP)

←

r

SP

←

SP-1, M(SP)

←

XP

SP

←

SP-1, M(SP)

←

XH

SP

←

SP-1, M(SP)

←

XL

SP

←

SP-1, M(SP)

←

YP

SP

←

SP-1, M(SP)

←

YH

SP

←

SP-1, M(SP)

←

YL

SP

←

SP-1, M(SP)

←

F

r

←

M(SP), SP

←

SP+1

XP

←

M(SP), SP

←

SP+1

XH

←

M(SP), SP

←

SP+1

XL

←

M(SP), SP

←

SP+1

YP

←

M(SP), SP

←

SP+1

Mne-

monic

Operation

↓

↓

↓

↓

↑

↓

↑

↓

↓

↓

↓

↓

Summary of Contents for S1C6200

Page 1: ...MF297 07 Core CPU Manual CMOS 4 BIT SINGLE CHIP MICROCOMPUTER S1C6200 6200A ...

Page 4: ......

Page 6: ......