COPYRIGHT © 2001 CANON INC. CANON CLC1000/1000S/3100 REV.2 MAY 2001 PRINTED IN JAPAN (IMPRIME AU JAPON)

3-105

3. OPERATION AND TIMING

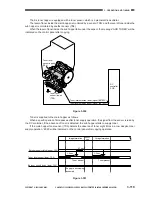

The DC bias is turned on and off, and the voltage is controlled as follows:

Developing bias enable signal (HVDCEN)=1

The DC bias output signal HVDC (between 0V and 12 V) is sent to the voltage control circuit.

The output from the transformer is controlled to suit the voltage of HVDC and is applied to

the developing cylinder.

The DC bias output signal (HVDC) and the developing bias enable signal (HVDCEN) have four channels

(for each color), and each of the four channels is controlled independently.

The changes in the developing DC bias

according to different voltage values are as shown

in Figure 3-530.

Figure 3-530

0V

11V

12V

-750V

-200V

HVDC

Developing DC bias

Summary of Contents for 1000S

Page 12: ......

Page 30: ......

Page 44: ......

Page 86: ......

Page 254: ......

Page 372: ......

Page 374: ......

Page 418: ......

Page 438: ......

Page 442: ......

Page 754: ......

Page 764: ......

Page 766: ......

Page 840: ...0501GR PRINTED IN JAPAN IMPRIME AU JAPON This publication is printed on 100 reprocessed paper ...