92

ATmega103(L)

0945G–09/01

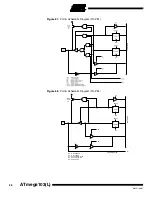

Figure 63.

Port D Schematic Diagram (Pin PD4)

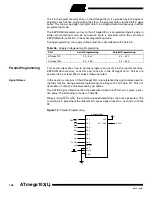

Figure 64.

Port D Schematic Diagram (Pin PD5)

DA

TA

B

U

S

D

D

Q

Q

RESET

RESET

C

C

WD

WP

RD

MOS

PULL-

UP

PD4

R

R

WP:

WD:

RL:

RP:

RD:

ACIC:

ACO:

WRITE PORTD

WRITE DDRD

READ PORTD LATCH

READ PORTD PIN

READ DDRD

COMPARATOR IC ENABLE

COMPARATOR OUTPUT

DDD4

PORTD4

NOISE CANCELER

EDGE SELECT

ICF1

ICNC1

ICES1

0

1

ACIC

ACO

RL

RP

DA

T

A

B

U

S

D

D

Q

Q

RESET

RESET

C

C

WD

WP

RD

MOS

PULL-

UP

PD5

R

R

WP:

WD:

RL:

RP:

RD:

WRITE PORTD

WRITE DDRD

READ PORTD LATCH

READ PORTD PIN

READ DDRD

DDD5

PORTD5

RL

RP