14

ATmega103(L)

0945G–09/01

Data Direct

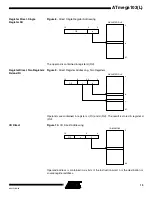

Figure 11.

Direct Data Addressing

A 16-bit data address is contained in the 16 LSBs of a 2-word instruction. Rd/Rr specify

the destination or source register.

Data Indirect with

Displacement

Figure 12.

Data Indirect with Displacement

Operand address is the result of the Y- or Z-register contents added to the address con-

tained in six bits of the instruction word.

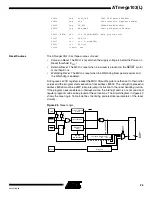

Data Indirect

Figure 13.

Data Indirect Addressing

Operand address is the contents of the X-, Y,- or the Z-register.

OP

Rr/Rd

16

31

15

0

16 LSBs

$0000

$FFFF

20 19

Data Space

Data Space

$0000

$FFFF

Y- OR Z-REGISTER

OP

a

n

0

0

5

6

10

15

15

Data Space

$0000

$FFFF

X-, Y- OR Z-REGISTER

0

15