80

ATmega103(L)

0945G–09/01

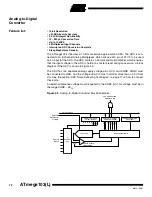

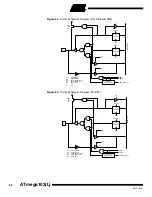

Figure 51.

External SRAM Access Cycle without Wait States

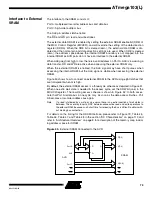

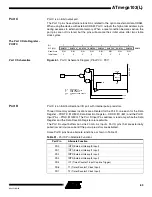

Figure 52.

External SRAM Access Cycle with Wait State

System Clock Ø

ALE

WR

RD

Data / Address [7..0]

Data / Address [7..0]

Address [15..8]

Address

Address

Address

T1

T2

T3

Prev. Address

Prev. Address

Prev. Address

Data

Data

Write

Read

Address

Address

System Clock Ø

ALE

WR

RD

Data / Address [7..0]

Data / Address [7..0]

Address [15..8]

Address

Address

Address

T1

T2

T3

T4

Prev. Address

Prev. Address

Prev. Address

Data

Data

Write

Read

Addr

.

Addr

.