Chapter 5: IP Core Architecture

5–9

Physical Layer

June 2012

Altera Corporation

Stratix V Hard IP for PCI Express

■

Transaction Layer Packet Checker—This block checks the integrity of the received

TLP and generates a request for transmission of an ACK/NAK DLLP.

■

TX Arbitration—This block arbitrates transactions, prioritizing in the following

order:

a. Initialize FC Data Link Layer packet

b. ACK/NAK DLLP (high priority)

c. Update FC DLLP (high priority)

d. PM DLLP

e. Retry buffer TLP

f. TLP

g. Update FC DLLP (low priority)

h. ACK/NAK FC DLLP (low priority)

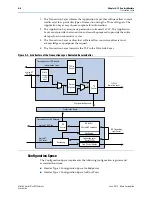

Physical Layer

The Physical Layer is the lowest level of the Stratix V Hard IP for PCI Express. It is the

layer closest to the link. It encodes and transmits packets across a link and accepts and

decodes received packets. The Physical Layer connects to the link through a

high-speed SERDES interface running at 2.5 Gbps for Gen1 implementations, at 2.5 or

5.0 Gbps for Gen2 implementations, and at 2.5, 5.0 or 8.0 Gbps for Gen 3

implementations.

The Physical Layer is responsible for the following actions:

■

Initializing the link

■

Scrambling/descrambling and 8B/10B encoding/decoding of 2.5 Gbps (Gen1),

5.0 Gbps (Gen2), or 128b/130b encoding/decoding of 8.0 Gbps (Gen3) per lane

■

Serializing and deserializing data

■

Operating the PIPE 3.0 Interface

■

Implementing auto speed negotiation (Gen2 and Gen3)

■

Transmitting and decoding the training sequence

■

Providing hardware autonomous speed control

■

Implementing auto lane reversal