5–4

Chapter 5: IP Core Architecture

Key Interfaces

Stratix V Hard IP for PCI Express

June 2012

Altera Corporation

credits become available. By tracking the credit consumed information and

calculating the credits available, the Application Layer can optimize performance by

selecting for transmission only the TLPs that have credits available. Refer to

for more information about the signals in this interface.

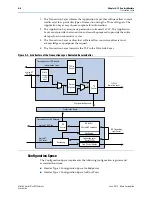

Avalon-MM Interface

In Qsys, the Stratix V Hard IP for PCI Express is available with either an Avalon-ST

interface or an Avalon-MM interface to the Application Layer. When you select the

Avalon-MM Stratix V Hard IP for PCI Express, an Avalon-MM bridge module

connects the PCI Express link to the system interconnect fabric. If you are not familiar

with the PCI Express protocol, variants using the Avalon-MM interface may be easier

to understand. A PCI Express to Avalon-MM bridge translates the PCI Express read,

write and completion TLPs into standard Avalon-MM read and write commands

typically used by master and slave interfaces. The PCI Express to Avalon-MM bridge

also translates Avalon-MM read, write and read data commands to PCI Express read,

write and completion TLPs.

Clocks and Reset

The

PCI Express Base Specification

requires an input reference clock, which is called

refclk

in this design. Although the

PCI Express Base Specification

stipulates that the

frequency of this clock be 100 MHz, the Hard IP also accepts a 125 MHz reference

clock as a convenience. You can specify the frequency of your input reference clock

using the parameter editor under the

System Settings

heading.

The

PCI Express Base Specification

also requires a system configuration time of 100 ms.

To meet this specification, the Stratix V Hard IP for PCI Express includes a hard reset

controller. This reset controller exits the reset state after the I/O ring of the device is

initialized. For more information about clocks and reset, refer to

, and

“Reset Signals and Status Signals” on

Local Management Interface (LMI Interface)

The LMI bus provides access to the PCI Express Configuration Space in the

Transaction Layer. For more LMI details, refer to

Hard IP Reconfiguration

The PCI Express reconfiguration bus allows you to dynamically change the

read-only

values stored in the Configuration Registers. For detailed information, refer to

IP Reconfiguration Interface” on page 6–44

.

Transceiver Reconfiguration

The transceiver reconfiguration interface allows you to dynamically reconfigure the

values of analog settings in the PMA block of the transceiver. Dynamic

reconfiguration is necessary to compensate for process variations at the 28 nm process

technology. The Altera Transceiver Reconfiguration Controller IP core provides access

to these analog settings. For more information about the transceiver reconfiguration

signals, refer to

“Physical Layer Interface Signals” on page 6–52

.