6-4

IM 760101-11E

Operation of the Standard Event Register

The standard event register is provided for eight

different kinds of event which can occur inside the

instrument. Bit 5 (ESB) of the status byte is set to “

1

”

when any of the bits in this register becomes “

1

” (or

when the corresponding bit of the standard event

enable register becomes “

1

”).

Examples

1. A query error occurs.

2. Bit 2 (QYE) is set to “

1

”.

3. Bit 5 (ESB) of the status byte is set to “

1

” if bit 2 of

the standard event enable register is “

1

”.

It is also possible to check what type of event has

occurred inside the instrument by reading the contents

of the standard event register.

Reading from the Standard Event Register

The contents of the standard event register can be

read by the

*ESR

command. After completion of the

read-out, the register will be cleared.

Clearing the Standard Event Register

ïThe standard event register is cleared in the following

three cases.

• When the contents of the standard event register

are read using

*ESR?

• When the

*CLS

command is received

• When power is turned ON again

6.3 Standard Event Register/6.4 Extended Event Register

6.4

Extended Event Register

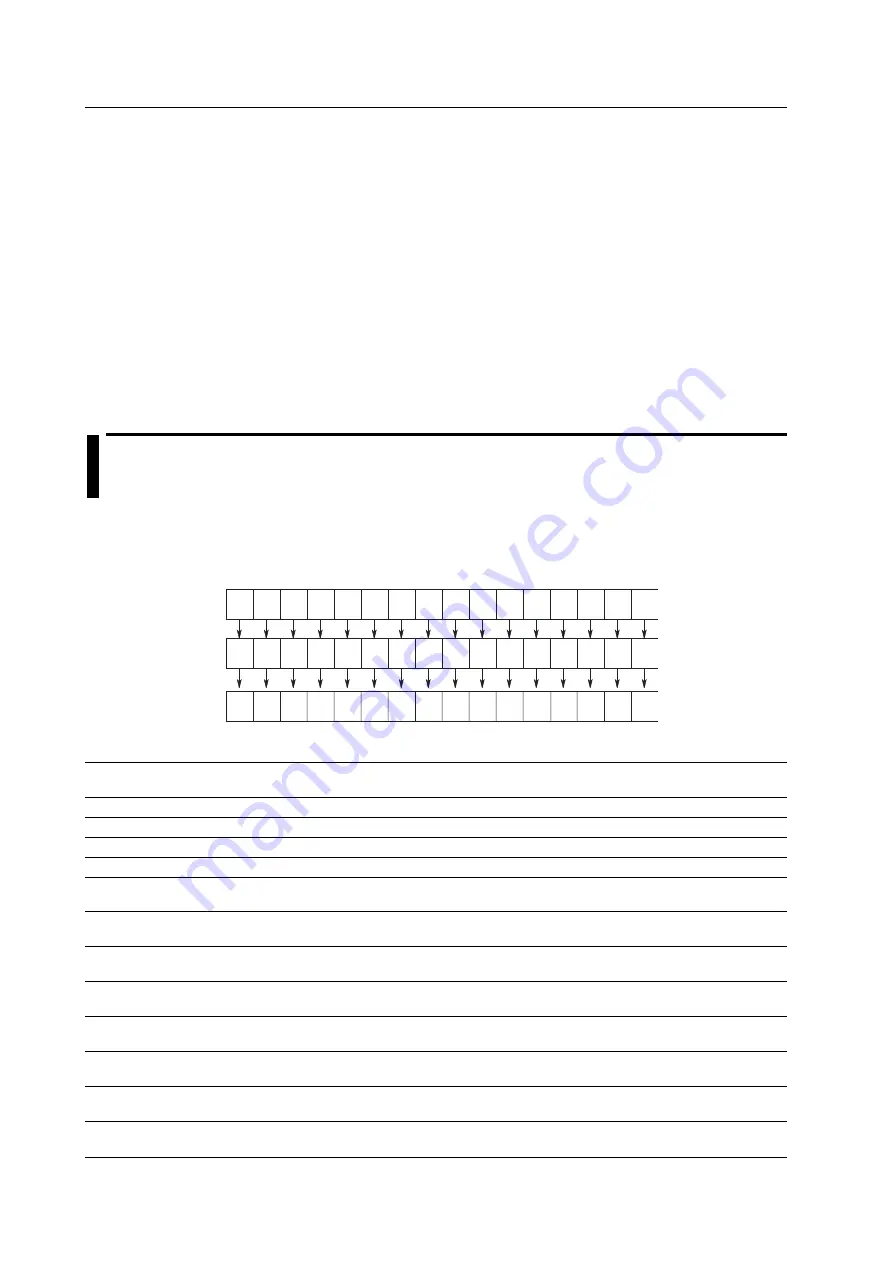

Reading the extended event register tells you whether changes in the condition register (reflecting internal

conditions) have occurred. A filter can be applied which allows you to decide which events are reported to

the extended event register.

ACS

6

PLLE

7

5

4

3

2

1

0

PRN

FOV

SRB

ITM

ITG

UPD

OVR1

8

OVR2

9

OVR3

10

OVR4

11

OVR5

12

OVR6

13

OVRM

14

POV

15

6

7

5

4

3

2

1

0

8

9

10

11

12

13

14

15

Condition register

:STATus:CONDition?

Transition filter

0

14

15

Extended event register

1

6

7

5

4

3

8

9

10

11

12

13

2

6

7

5

4

3

2

1

8

9

10

11

12

13

14

15

16

:STATus:FILTer<x>

{RISE|FALL|BOTH|NEVer}

:STATus:EESR?

FILTer<x> ->

The meaning of each bit of the condition register is as follows.

Bit 0

UPD (Updating)

Set to “

1

” when the measured data is being updated.

The falling edge of UPD (1 -> 0) signifies the end of the updating.

Bit 1

ITG (Integrate Busy)

Set to “

1

” while integration is in progress.

Bit 2

ITM (Integrate Timer Busy)

Set to “

1

” while the integration timer is running.

Bit 3

SRB (Store/Recall Busy)

Set to “

1

” while storing or recalling data.

Bit 4

FOV (Frequency Over)

Set to “

1

” when the frequency is in error.

Bit 5

PRN (Printing)

Set to “

1

” while the internal printer is in operation or data is being output to the

external printer (Centronics or network printer).

Bit 6

ACS (Accessing)

Set to “

1

” while the floppy disk, internal hard disk, or external disk drive (SCSI or

network device) is being accessed.

Bit 7

PLLE

Set to “

1

” when there is no input to the PLL source and synchronization cannot be

(PLL Source Input Error)

achieved during harmonic measurement.

Bit 8

OVR1

Set to “

1

” when the voltage or current of element 1 is over the range.

(Element1 Measured Data Over)

Bit 9

OVR2

Set to “

1

” when the voltage or current of element 2 is over the range.

(Element1 Measured Data Over)

Bit 10

OVR3

Set to “

1

” when the voltage or current of element 3 is over the range.

(Element3 Measured Data Over)

Bit 11

OVR4

Set to “

1

” when the voltage or current of element 4 is over the range.

(Element4 Measured Data Over)

Содержание wt1600

Страница 1: ...Digital Power Meter Communication Interface IM 760101 11E 4th Edition ...

Страница 131: ...7 2 IM 760101 11E 7 2 Sample Program Image ...

Страница 138: ...Sample Program 7 9 IM 760101 11E 7 7 4 Output of Normal Measurement Data ...

Страница 142: ...Sample Program 7 13 IM 760101 11E 7 7 5 Output of Harmonic Measurement Data ...