SARA-N2 / N3 series - System integration manual

UBX-17005143 - R13

System description

Page 25 of 95

C1-Public

SARA-N3 series modules include the

RXD

,

TXD

,

CTS

,

RTS

,

DTR

,

DSR

,

DCD

,

RI

pins as main primary

UART interface, supporting:

•

AT communication

•

FW upgrades by means of the FOAT feature

The main characteristics of the SARA-N3 series modules main primary UART interface are the

following:

•

Serial port with RS-232 functionality conforming to ITU-T V.24 recommendation

•

It operates at

V_INT

level, with voltage value set as per external

VSEL

pin configuration

o

0 V for low data bit or ON state

o

V_INT

, i.e. 1.8 V or 2.8 V, for high data bit or OFF state

•

Data lines (

RXD

as module data output,

TXD

as module data input) are provided

•

Hardware flow control lines (

CTS

as output,

RTS

as input) and

RI

output line are provided, and they

can be alternatively configured as described in section

(for more details see also the SARA-N2

/ SARA-N3 series AT commands manual

•

The modem status and control lines (

DTR

as input,

DSR

as output,

DCD

as output) are not

supported by

“

00

”

product versions

•

Hardware flow control disabled by default

•

One-shot automatic baud rate detection enabled by default

•

UART works in low power idle mode, supporting 4800, 9600, 19200, 38400, 57600 b/s baud rates

•

8N1 default frame format

The UART interface provides RS-232 functionality conforming to the ITU-T V.24 Recommendation

(more details available in ITU recommendation

): SARA-N2 / N3 series modules are designed to

operate as a cellular modem, which represents the Data Circuit-terminating Equipment (DCE)

according to ITU-T V.24 recommendation

. The application processor connected to the module

through the UART interface represents the Data Terminal Equipment (DTE).

The UART interface settings can be suitably configured by AT commands (for more details, see the

SARA-N2 / SARA-N3 series AT commands manual

☞

The signal names of the SARA-N2 / N3 series

modules’ UART interface

conform to the ITU-T V.24

recommendation

: e.g. the

TXD

line represents the data transmitted by the DTE (application

processor data line output) and received by the DCE (module data line input).

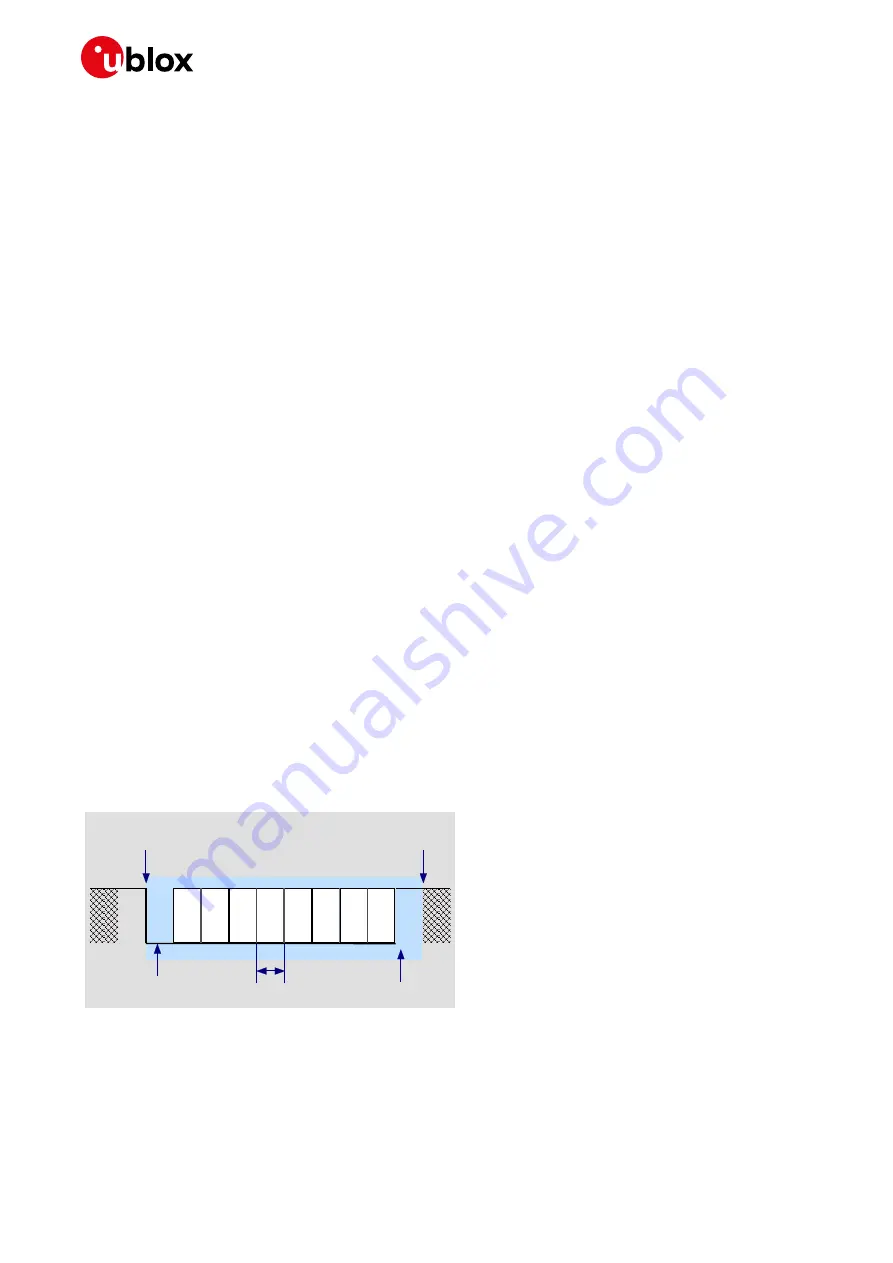

describes the 8N1 frame format.

D0

D1

D2

D3

D4

D5

D6

D7

Start of 1-Byte

transfer

Start Bit

(Always 0)

Possible Start of

next transfer

Stop Bit

(Always 1)

t

bit

= 1/(Baudrate)

Normal Transfer, 8N1

Figure 12: Description of UART default frame format (8N1) with fixed baud rate