LISA-U1 series - System Integration Manual

3G.G2-HW-10002-3

Preliminary

System description

Page 54 of 125

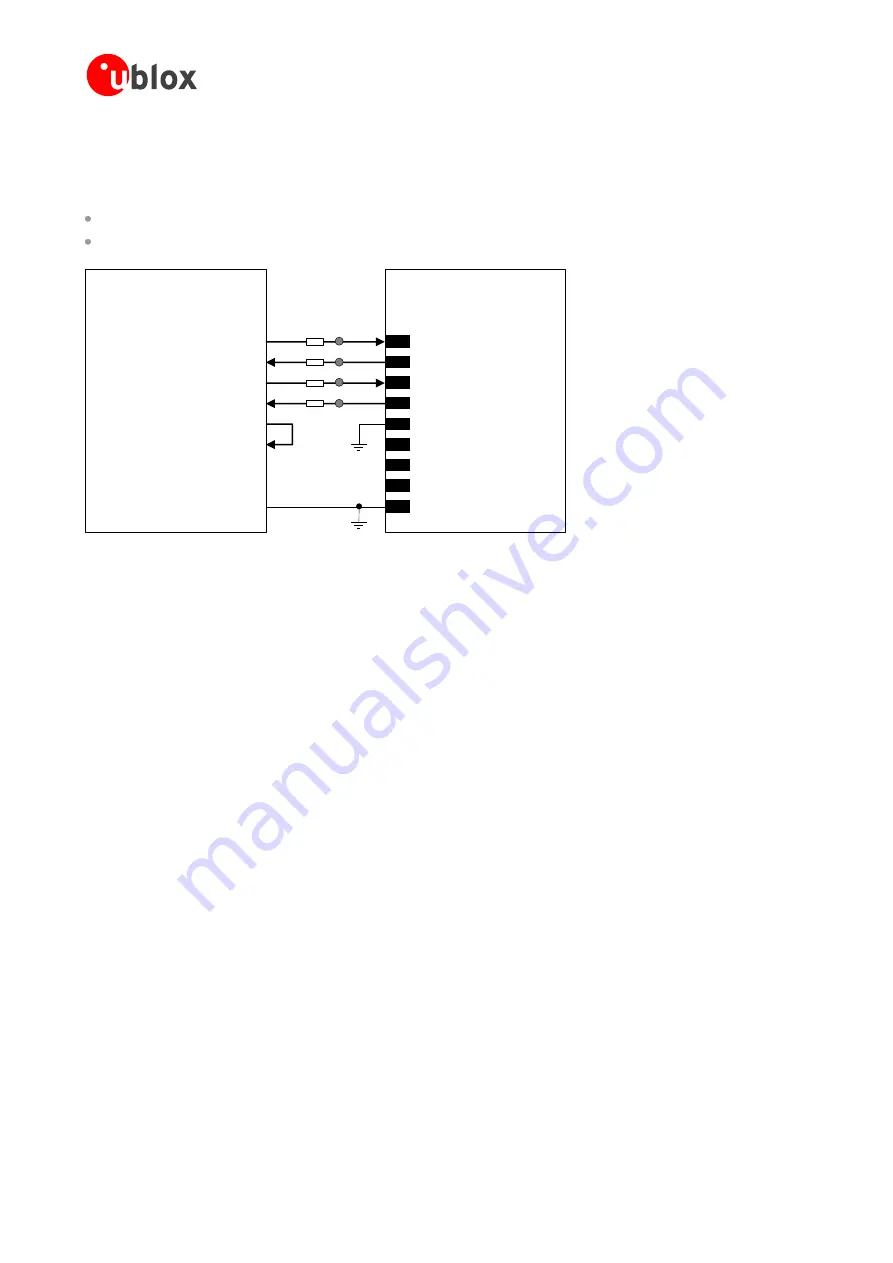

Providing the TxD, RxD, RTS and CTS lines only (not using the complete V.24 link)

If the functionality of the

DSR

,

DCD

,

RI

and

DTR

lines is not required in the application, or the lines are not

available, the application circuit described in Figure 28 must be implemented:

Connect the module

DTR

input line to GND, since the module requires

DTR

active (low electrical level)

Leave

DSR

,

DCD

and

RI

lines of the module unconnected and floating

LISA-U1 series

(DCE)

TxD

Application Processor

(DTE)

RxD

RTS

CTS

DTR

DSR

RI

DCD

GND

15

TXD

12

DTR

16

RXD

13

RTS

14

CTS

9

DSR

10

RI

11

DCD

GND

0

Ω

0

Ω

TP

TP

0

Ω

0

Ω

TP

TP

Figure 28: UART interface application circuit with partial V.24 link (5-wire) in the DTE/DCE serial communication

If only

TxD

,

RxD

,

RTS

and

CTS

lines are provided as described in Figure 28 the procedure to enable power

saving depends on the HW flow-control status. If HW flow-control is enabled (AT&K3, that is the default setting)

power saving will be activated by AT+UPSV=1. Through this configuration, when the module is in idle-mode,

data transmitted by the DTE will be buffered by the DTE and will be correctly received by the module when

active-mode is entered.

If the HW flow-control is disabled (AT&K0), the power saving can be enabled by AT+UPSV=2. The module is in

idle-mode until a high-to-low (i.e. OFF-to-ON) transition on the

RTS

input line will switch the module from

idle-mode to active-mode in 20 ms. The module will be forced in active-mode if the

RTS

input line is held in the

ON state.