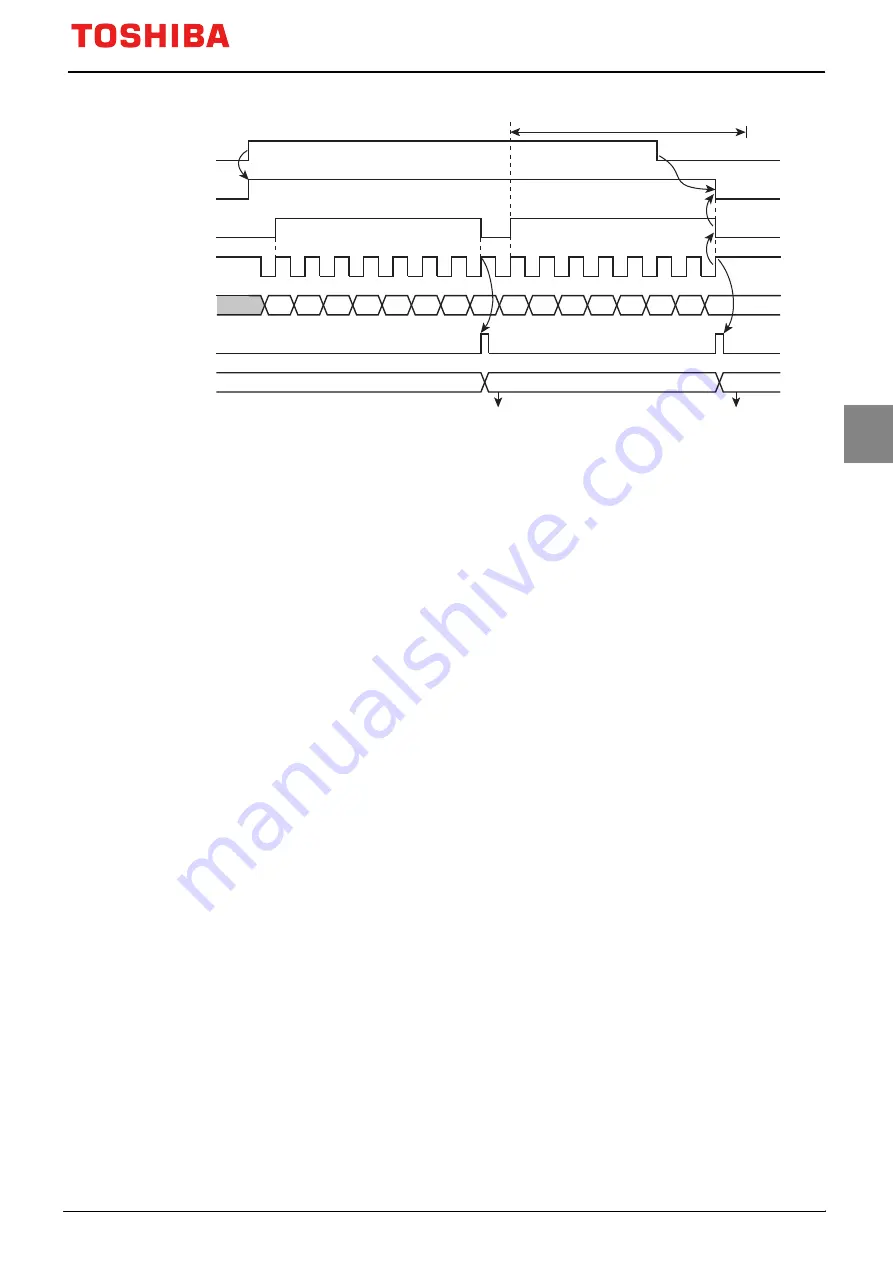

<SIOF>

<SIOS>

<SEF>

a

1

a

0

a

2

a

3

a

4

a

5

a

6

a

7

b

0

b

1

b

2

b

3

b

4

b

5

b

6

b

7

b

a

Clear <SIOS>

Read receive data

Read receive data

SCK pin(output)

SI pin

INTSBI

interrupt request

SBIDBR

Figure 13-19 Receive Mode (Example: Internal Clock)

13.8.2.3 8-bit transmit/receive mode

Set the control register to the transfer/receive mode. Then writing the transmit data to SBIDBR and set-

ting SBICR1<SIOS> to "1" enables transmission and reception.The transmit data is output through the

SOx pin at the falling of the serial clock, and the received data is taken in through the SI pin at the rising

of the serial clock, with the least-significant bit (LSB) first. Once the shift register is loaded with the 8-

bit data, it transfers the received data to SBIDBR and the INTSBI interrupt request is generated.The inter-

rupt service program reads the received data from the data buffer register and writes the next transmit da-

ta. Because SBIDBR is shared between transmit and receive operations, the received data must be read be-

fore the next transmit data is written.

In the internal clock operation, the serial clock will be automatically in the wait state until the received

data is read and the next transmit data is written.

In the external clock mode, shift operations are executed in synchronization with the external serial

clock. Therefore, the received data must be read and the next transmit data must be written before the

next shift operation is started.The maximum data transfer rate for the external clock operation varies depend-

ing on the maximum latency between when the interrupt request is generated and when the transmit data

is written.

At the beginning of transmission, the same value as in the last bit of the previously transmitted data is out-

put in a period from setting <SIOF> to "1" to the falling edge of SCK.

Transmission and reception can be terminated by clearing <SIOS> to "0" or setting SBICR1<SIOINH>

to "1" in the INTSBI interrupt service program. If <SIOS> is cleared, transmission and reception contin-

ue until the received data is fully transferred to SBIDBR. The program checks SBISR<SIOF> to deter-

mine whether transmission and reception have come to an end. <SIOF> is cleared to "0" at the end of trans-

mission and reception.If <SIOINH> is set to "1", the transmission and reception is aborted immediately

and <SIOF> is cleared to "0".

Note:

The contents of SBIDBR will not be retained after the transfer mode is changed. The ongo-

ing transmission and reception must be completed by clearing <SIOS> to "0" and the last re-

ceived data must be read before the transfer mode is changed.

TMPM3V6/M3V4

Page 307

2019-02-06

Содержание TMPM3V4

Страница 1: ...32 Bit RISC Microcontroller TX03 Series TMPM3V6 M3V4 ...

Страница 2: ... 2019 Toshiba Electronic Devices Storage Corporation ...

Страница 7: ...Revision History Date Revision Comment 2019 02 06 1 First Release ...

Страница 8: ......

Страница 22: ...xiv ...

Страница 52: ...TMPM3V6 M3V4 3 Processor Core 3 6 Exclusive access Page 30 2019 02 06 ...

Страница 148: ...TMPM3V6 M3V4 7 Exceptions 7 6 Exception Interrupt Related Registers Page 126 2019 02 06 ...

Страница 178: ...TMPM3V6 M3V4 9 Input Output port 9 2 Block Diagrams of Ports Page 156 2019 02 06 ...

Страница 206: ...TMPM3V6 M3V4 10 16 bit Timer Event Counters TMRB 10 7 Applications using the Capture Function Page 184 2019 02 06 ...

Страница 232: ...TMPM3V6 M3V4 11 Universal Asynchronous Receiver Transmitter Circuit UART 11 4 Operation Description Page 210 2019 02 06 ...

Страница 354: ...TMPM3V6 M3V4 14 Synchronous Serial Port SSP 14 6 Frame Format Page 332 2019 02 06 ...

Страница 419: ...TMPM3V6 M3V4 Page 397 2019 02 06 ...

Страница 420: ...TMPM3V6 M3V4 16 Analog Digital Converter ADC 16 6 Timing chart of AD conversion Page 398 2019 02 06 ...

Страница 462: ...TMPM3V6 M3V4 21 Watchdog Timer WDT 21 5 Control register Page 440 2019 02 06 ...

Страница 510: ...TMPM3V6 M3V4 22 Flash Memory Operation 22 4 Programming in the User Boot Mode Page 488 2019 02 06 ...

Страница 538: ...TMPM3V6 M3V4 25 Electrical Characteristics 25 7 Recommended Oscillation Circuit Page 516 2019 02 06 ...

Страница 541: ...26 3 TMPM3V4FWUG TMPM3V4FSUG Type LQFP64 P 1010 0 50E LPHQVLRQV TMPM3V6 M3V4 Page 519 2019 02 06 ...

Страница 544: ......