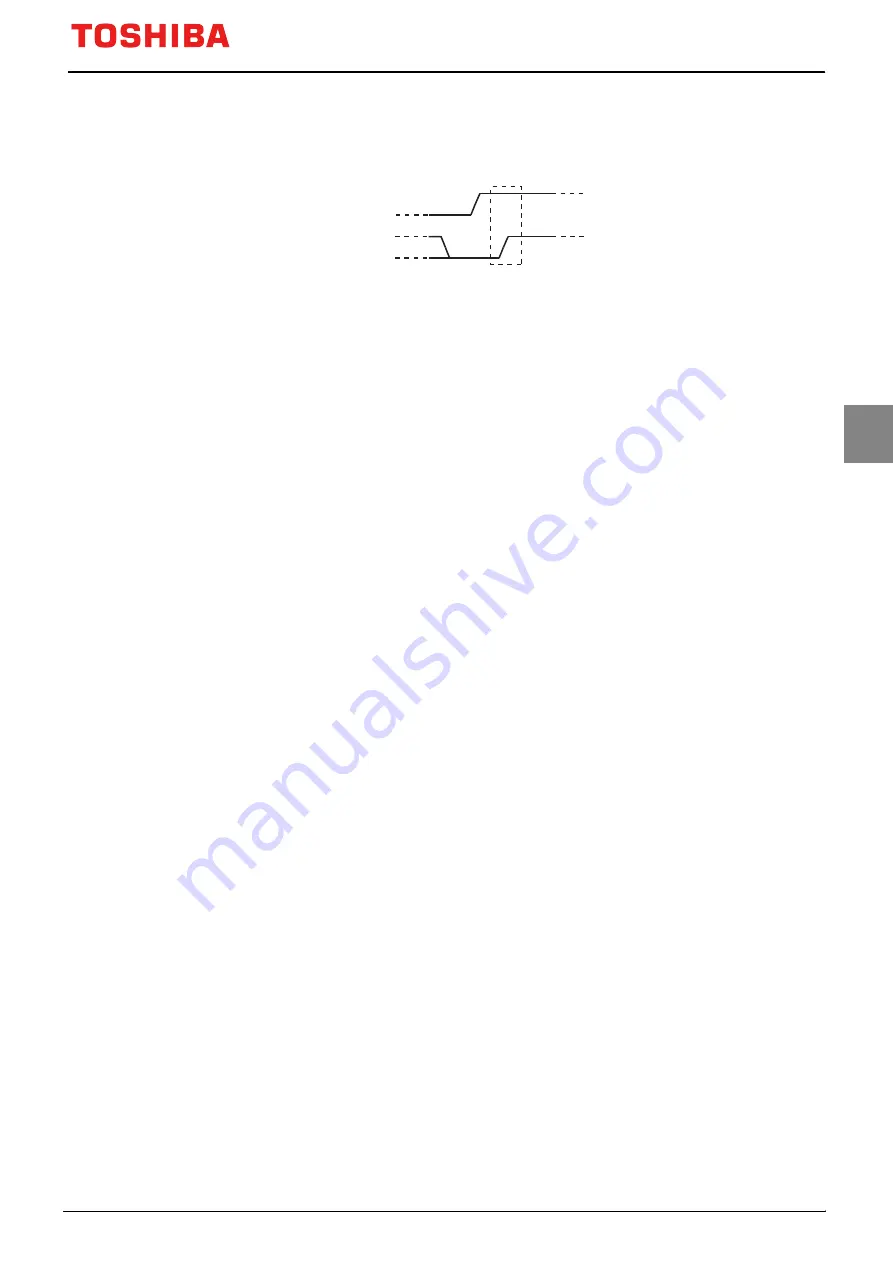

If SCL bus line is pulled "Low" by other devices when the stop condition is generated, the stop condition

is generated after the SCL line is released.

SCL line

SDA line

Stop condition

Figure 13-6 Generating the Stop Condition

SBISR<BB> can be read to check the bus state. <BB> is set to "1" when the start condition is detected on

the bus (the bus is busy), and cleared to "0" when the stop condition is detected (the bus is free).

13.5.9 Interrupt Service Request and Release

In master mode, a serial bus interface request (INTSBI) is generated when the transfer of the number of

clock cycles set by <BC> and <ACK> is completed.

In slave mode, INTSBI is generated under the following conditions.

・

After output of the acknowledge signal which is generated when the received slave address match-

es the slave address set to SBII2CAR<SA[6:0]>.

・

After the acknowledge signal is generated when a general-call address is received.

・

When the slave address matches or a data transfer is completed after receiving a general-call address.

In the address recognition mode (<ALS> = "0"), INTSBI is generated when the received slave address match-

es the values specified at SBII2CAR or when a general-call (eight bits data following the start condition is

all "0") is received.

When an interrupt request (INTSBI) is generated, SBICR2<PIN> is cleared to "0". While <PIN> is

cleared to "0", the SBI pulls the SCL line to the "Low" level.

<PIN> is set to "1" when data is written to or read from SBIDBR. It takes a period of t

LOW

for the SCL

line to be released after <PIN> is set to "1". When the program writes "1" to <PIN>, it is set to "1". Howev-

er, writing "0" does not clear this bit to "0".

Note:

When arbitration occurs while a slave address and direction bit are transferred in the master mode,

<PIN> is cleared to "0" and INTSBI occurs. This does not relate to whether a slave address match-

es <SA>.

13.5.10 Arbitration Lost Detection Monitor

The I2C bus has the multi-master capability (there are two or more masters on a bus), and requires the bus

arbitration procedure to ensure correct data transfer.

A master that attempts to generate the start condition while the bus is busy loses bus arbitration, with no

start condition occurring on the SDA and SCL lines.The I2C-bus arbitration takes place on the SDA line.

The arbitration procedure for two masters on a bus is shown below.

TMPM3V6/M3V4

Page 283

2019-02-06

Содержание TMPM3V4

Страница 1: ...32 Bit RISC Microcontroller TX03 Series TMPM3V6 M3V4 ...

Страница 2: ... 2019 Toshiba Electronic Devices Storage Corporation ...

Страница 7: ...Revision History Date Revision Comment 2019 02 06 1 First Release ...

Страница 8: ......

Страница 22: ...xiv ...

Страница 52: ...TMPM3V6 M3V4 3 Processor Core 3 6 Exclusive access Page 30 2019 02 06 ...

Страница 148: ...TMPM3V6 M3V4 7 Exceptions 7 6 Exception Interrupt Related Registers Page 126 2019 02 06 ...

Страница 178: ...TMPM3V6 M3V4 9 Input Output port 9 2 Block Diagrams of Ports Page 156 2019 02 06 ...

Страница 206: ...TMPM3V6 M3V4 10 16 bit Timer Event Counters TMRB 10 7 Applications using the Capture Function Page 184 2019 02 06 ...

Страница 232: ...TMPM3V6 M3V4 11 Universal Asynchronous Receiver Transmitter Circuit UART 11 4 Operation Description Page 210 2019 02 06 ...

Страница 354: ...TMPM3V6 M3V4 14 Synchronous Serial Port SSP 14 6 Frame Format Page 332 2019 02 06 ...

Страница 419: ...TMPM3V6 M3V4 Page 397 2019 02 06 ...

Страница 420: ...TMPM3V6 M3V4 16 Analog Digital Converter ADC 16 6 Timing chart of AD conversion Page 398 2019 02 06 ...

Страница 462: ...TMPM3V6 M3V4 21 Watchdog Timer WDT 21 5 Control register Page 440 2019 02 06 ...

Страница 510: ...TMPM3V6 M3V4 22 Flash Memory Operation 22 4 Programming in the User Boot Mode Page 488 2019 02 06 ...

Страница 538: ...TMPM3V6 M3V4 25 Electrical Characteristics 25 7 Recommended Oscillation Circuit Page 516 2019 02 06 ...

Страница 541: ...26 3 TMPM3V4FWUG TMPM3V4FSUG Type LQFP64 P 1010 0 50E LPHQVLRQV TMPM3V6 M3V4 Page 519 2019 02 06 ...

Страница 544: ......