17

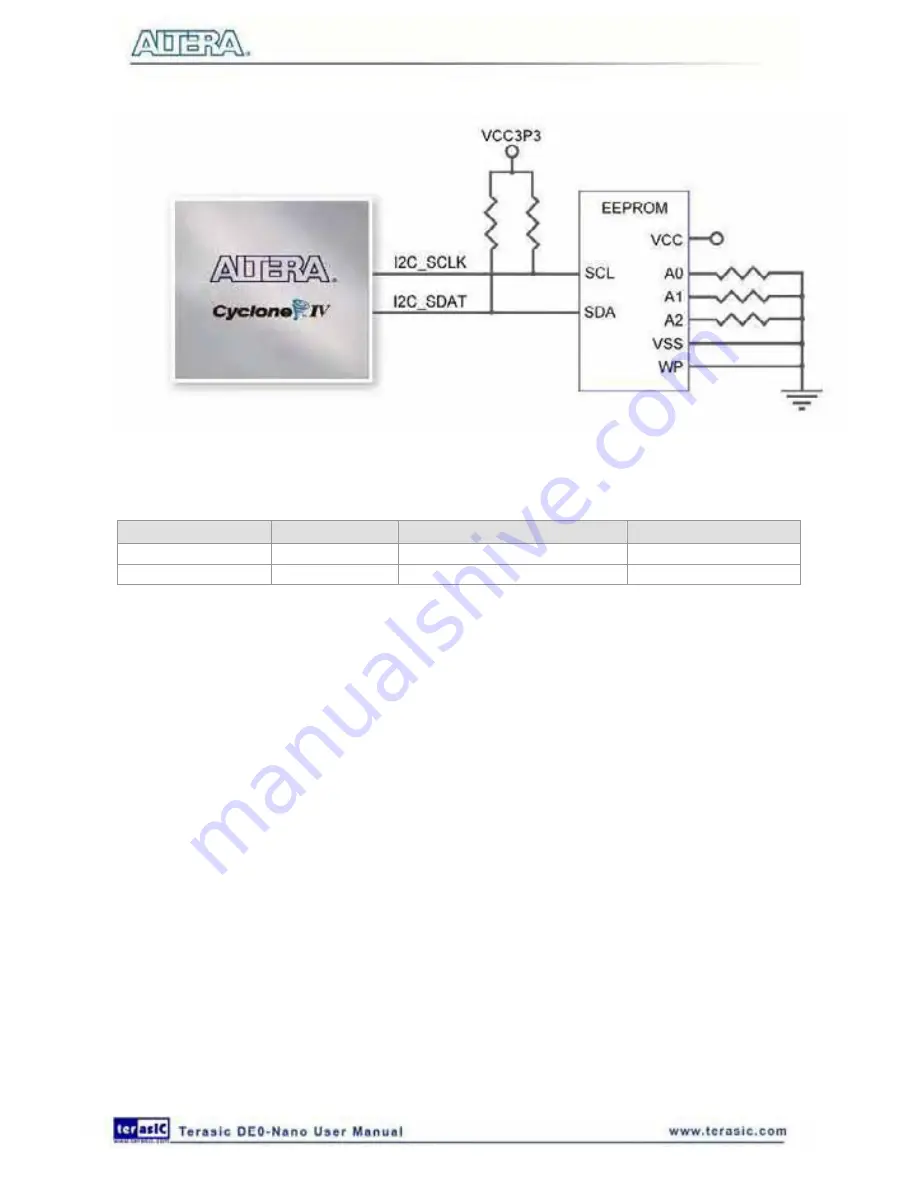

Figure 3-7 Connections between FPGA and EEPROM

Table 3-5 Pin Assignments for I2C Serial EEPROM

Signal Name

FPGA Pin No.

Description

I/O Standard

I2C_SCLK

PIN_F2

EEPROM clock

3.3V

I2C_SDAT

PIN_F1

EEPROM data

3.3V

3

3

.

.

5

5

E

E

x

x

p

p

a

a

n

n

s

s

i

i

o

o

n

n

H

H

e

e

a

a

d

d

e

e

r

r

s

s

The DE0-Nano board provides two 40-pin expansion headers. Each header connects directly to 36

pins of the Cyclone IV E FPGA, and also provides DC +5V (VCC5), DC +3.3V (VCC33), and two

GND pins.

Figure 3-8

shows the I/O distribution of the GPIO connectors.

Содержание De0-Nano

Страница 1: ...1 ...

Страница 4: ...4 9 3 Revision History 155 9 4 Copyright Statement 155 ...

Страница 44: ...44 Figure 6 5 Browse to find the location Figure 6 6 There is no need to test the driver ...

Страница 90: ...90 Figure 7 14 Add NIOS II Processor ...

Страница 91: ...91 Figure 7 15 Nios II Processor 9 Click Finish to return to main window as shown in Figure 7 16 ...

Страница 93: ...93 Figure 7 17 Rename the CPU 1 Figure 7 18 Rename the CPU 2 ...

Страница 98: ...98 Figure 7 23 Add On Chip Memory ...

Страница 100: ...100 Figure 7 25 Update Total memory size ...

Страница 102: ...102 Figure 7 28 Update CPU settings ...

Страница 104: ...104 Figure 7 30 Add PIO ...

Страница 106: ...106 Figure 7 32 PIO 21 Rename pio_0 to pio_led as shown in Figure 7 33 Figure 7 33 Rename PIO ...

Страница 113: ...113 Figure 7 43 Input verilog Text Figure 7 44 Open DE0_NANO_SOPC v ...

Страница 146: ...146 Figure 8 16 Display Progress and Result Information for the SDRAM Demonstration ...

Страница 150: ...150 Figure 9 3 Select Devices Page ...

Страница 151: ...151 Figure 9 4 Convert Programming Files Page ...