117

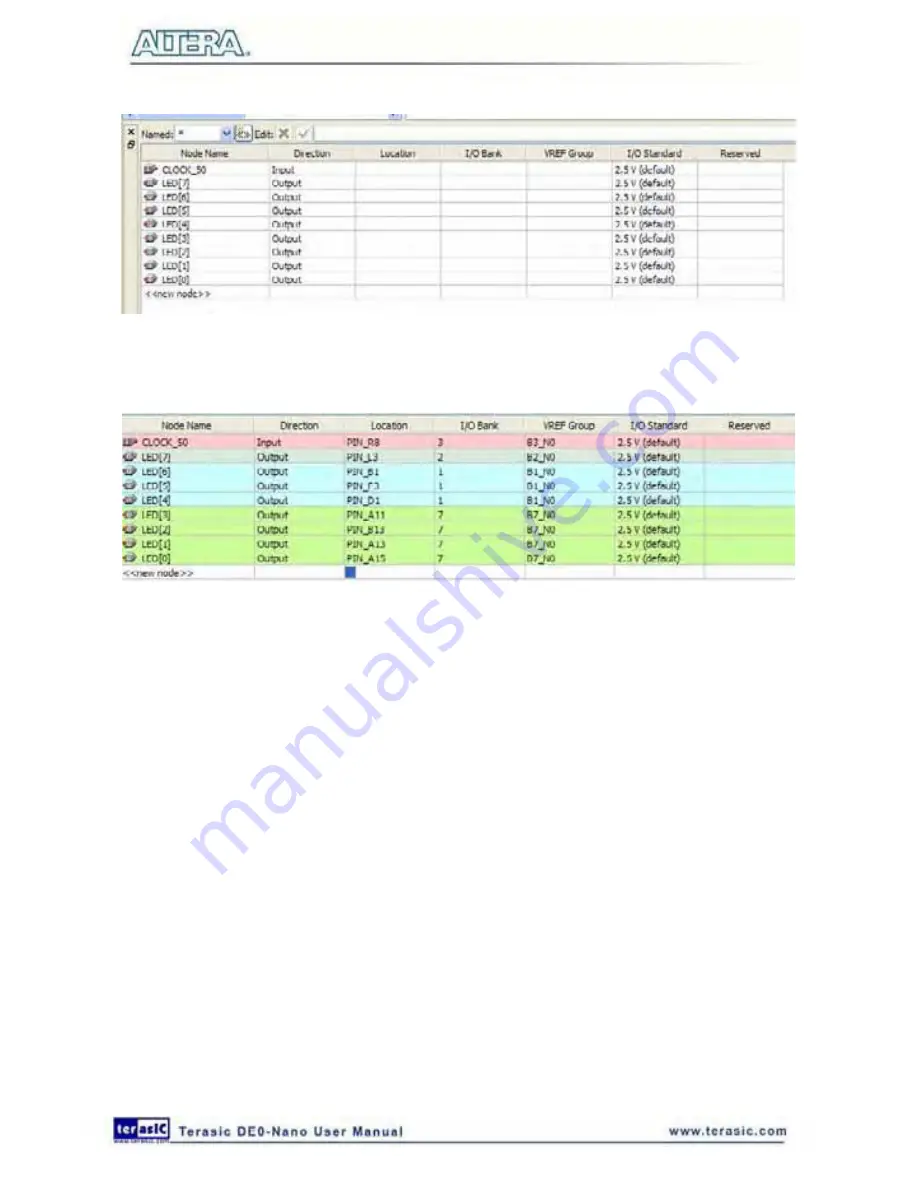

Figure 7-51 Blank Pins

39. Input Location values as shown in

Figure 7-52

.

Figure 7-52 Set Pins

40. Close the pin planner and recompile the project.

7

7

.

.

3

3

D

D

o

o

w

w

n

n

l

l

o

o

a

a

d

d

t

t

h

h

e

e

H

H

a

a

r

r

d

d

w

w

a

a

r

r

e

e

D

D

e

e

s

s

i

i

g

g

n

n

This section describes how to download the configuration file to the board.

Download the FPGA configuration file (i.e. the SRAM Object File (.sof) that contains the NIOS II

based system) to the board by performing the following steps:

1. Connect the board to the host computer via the USB download cable.

2. Start the

NIOS II IDE

.

3. After the welcome page appears, click

Workbench

.

4. Select

Tools

>

Quartus II Programmer

.

5. Click

Auto Detect

. The device on your development board should be detected automatically.

6. Click the top row to highlight it.

Содержание De0-Nano

Страница 1: ...1 ...

Страница 4: ...4 9 3 Revision History 155 9 4 Copyright Statement 155 ...

Страница 44: ...44 Figure 6 5 Browse to find the location Figure 6 6 There is no need to test the driver ...

Страница 90: ...90 Figure 7 14 Add NIOS II Processor ...

Страница 91: ...91 Figure 7 15 Nios II Processor 9 Click Finish to return to main window as shown in Figure 7 16 ...

Страница 93: ...93 Figure 7 17 Rename the CPU 1 Figure 7 18 Rename the CPU 2 ...

Страница 98: ...98 Figure 7 23 Add On Chip Memory ...

Страница 100: ...100 Figure 7 25 Update Total memory size ...

Страница 102: ...102 Figure 7 28 Update CPU settings ...

Страница 104: ...104 Figure 7 30 Add PIO ...

Страница 106: ...106 Figure 7 32 PIO 21 Rename pio_0 to pio_led as shown in Figure 7 33 Figure 7 33 Rename PIO ...

Страница 113: ...113 Figure 7 43 Input verilog Text Figure 7 44 Open DE0_NANO_SOPC v ...

Страница 146: ...146 Figure 8 16 Display Progress and Result Information for the SDRAM Demonstration ...

Страница 150: ...150 Figure 9 3 Select Devices Page ...

Страница 151: ...151 Figure 9 4 Convert Programming Files Page ...