13. I2C Registers > Register Descriptions

430

Tsi576 User Manual

June 6, 2016

Integrated Device Technology

www.idt.com

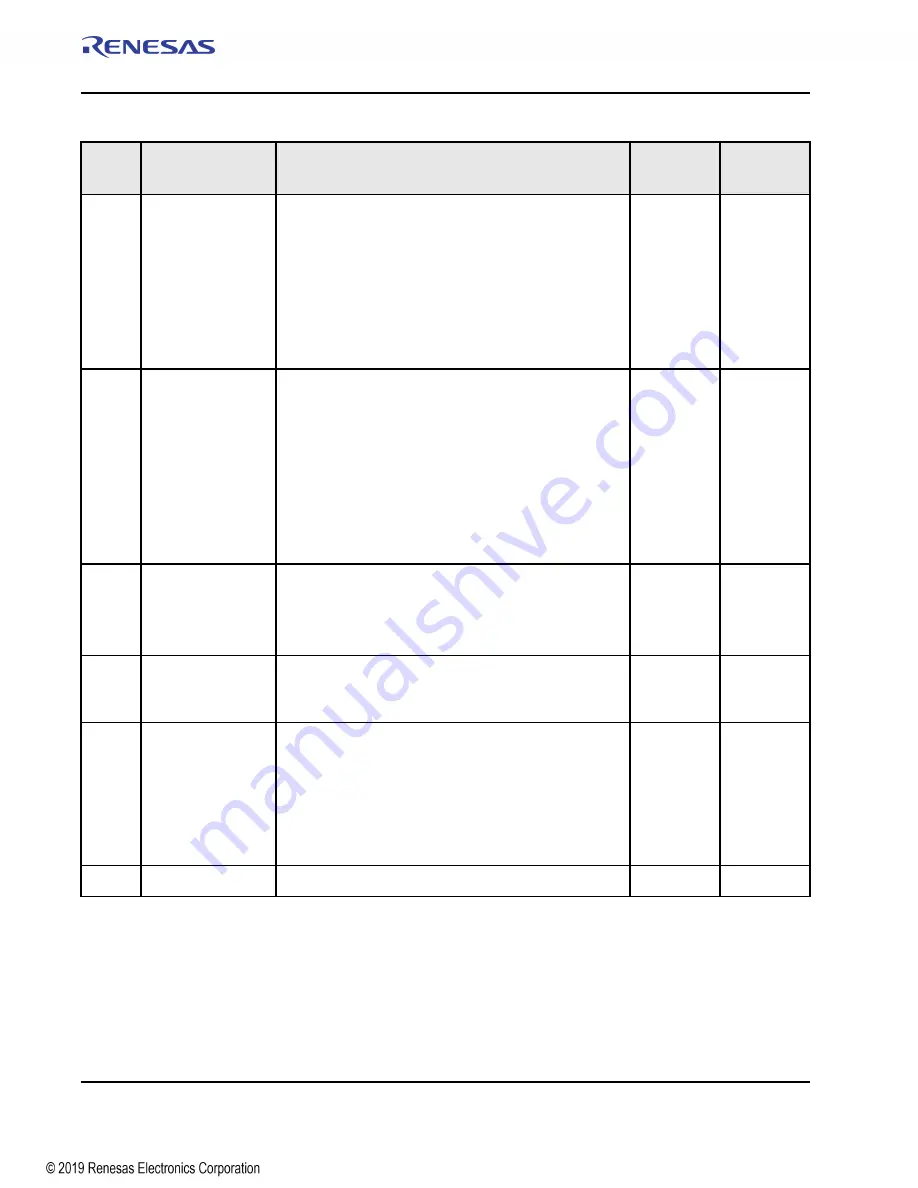

04

SLV_WAIT

Slave Wait

0 = Slave is not waiting for a STOP or RESTART

1 = Slave is waiting for a STOP or RESTART

This bit is clear if the bus is not active or the slave address is

being received or the slave is active. This bit is set if the bus

is active but the slave is not active and the slave address is

not being received.

Note: This bit is zeroed on a reset controlled by the

.

R

0

05:06

SLV_PHASE

Slave Phase

00 = Slave address being received (even if slave interface is

disabled using SLV_EN).

01 = Peripheral address being received

10 = Data incoming (write from external master)

11 = Data outgoing (read by external master)

At the end of a slave operation, this field will hold its value

until the next START/RESTART. If a slave operation aborts,

this field will qualify where in the transaction the error

occurred.

R

0x0

07

SLV_AN

Slave Ack/Nack

0 = Slave transaction is not in the ACK/NACK bit of a byte

1 = Slave transaction is in the ACK/NACK bit of a byte

This qualifies the SLV_PHASE field.

R

0

08:15

SLV_PA

Slave Peripheral Address

This field indicates the current peripheral address that is

used when the Tsi576 is accessed by an external master.

R

0x00

16

MST_ACTIVE

Master Active

0 = No master operation in progress

1 = Master operation is in progress

This status is the same as the START bit in the

Note: This bit is zeroed on a reset controlled by the

.

R

0

17:19

Reserved

Reserved

R

0

(Continued)

Bits

Name

Description

Type

Reset

Value

Содержание IDT Tsi576

Страница 1: ...IDT Tsi576 Serial RapidIO Switch User Manual June 6 2016 Titl...

Страница 20: ...About this Document 20 Tsi576 User Manual June 6 2016 Integrated Device Technology www idt com...

Страница 34: ...1 Functional Overview JTAG Interface 34 Tsi576 User Manual June 6 2016 Integrated Device Technology www idt com...

Страница 102: ...4 Internal Switching Fabric Packet Queuing 102 Tsi576 User Manual June 6 2016 Integrated Device Technology www idt com...

Страница 230: ...11 Signals Pinlist and Ballmap 230 Tsi576 User Manual June 6 2016 Integrated Device Technology www idt com...

Страница 506: ...B Clocking P_CLK Programming 506 Tsi576 User Manual June 6 2016 Integrated Device Technology www idt com...

Страница 528: ...Index 528 Tsi576 User Manual June 6 2016 Integrated Device Technology www idt com...