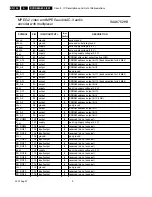

Circuit-, IC Descriptions and List of Abbreviations

EN 207

DVDR880-890 /0X1

9.

Composite video/Luminance input to Video Input Processor

CVBS_Y_IN_C

Composite video/Luminance input to Video Input Processor

D_ADDR(10:0)

Address bus

D_DATA(29:0)

Data bus

D_EMPRESS(15:0)

SDRAM data input/output of EMPRESS

D_PAR_D(7:0)

Front-end parallel interface data (record)

D_PAR_DVALID

Front-end parallel interface data valid

D_PAR_REQ

Front-end parallel interface request

D_PAR_STR

Front-end parallel interface strobe

D_PAR_SYNC

Front-end parallel interface sync

DV_IN_CLK

Digital Video in clock from DVIO board

DV_IN_DATA(7:0)

Digital Video in data bus from DVIO board

DV_IN_HS

Digital Video in horizontal synchronisation from DVIO board

DV_IN_VS

Digital Video in vertical synchronisation from DVIO board

EMI_A(21:1)

External Memory Interface Address Bus(Host Decoder)

EMI_BE0N

External Memory Interface Lower byte enable(Host Decoder)

EMI_BE1N

External Memory Interface Upper byte enable(Host Decoder)

EMI_CAS0N

External Memory Interface SDRAM column address

strobe(Host Decoder)

EMI_CE1N

External Memory Interface VSM Lower bank enable

EMI_CE2N

External Memory Interface VSM Higher bank enable

EMI_CE3N

External Memory Interface flash IC's enable

EMI_D(15:0)

External Memory Interface Data Bus(Host Decoder)

EMI_PROCCLK

External Memory Interface Processor Clock(Host Decoder)

EMI_RWN

External Memory Interface Read/Write control signal(Host

Decoder)

EMI_WAIT

External Memory Interface Wait state request(Host Decoder)

EMPRESS_BOOT

EMPRESS BOOT select input

EMPRESS_IRQN

EMPRESS Interrupt request output

FLASH_OEN

FLASH output enable control signal

G_IN_VIP

Video green input to Video Input Processor

G_OUT

Video green output from Host Decoder

G_OUT_B

Filtered green video output from Host Decoder

GNDD

Digital Ground

HD_M_AD(13:0)

Host Decoder SDRAM address bus

HD_M_CASN

Host Decoder SDRAM column address strobe

HD_M_CLK

Host Decoder SDRAM clock

HD_M_CS0N

Host Decoder SDRAM chip select

HD_M_DQ(15:0)

Host Decoder SDRAM data bus

HD_M_DQML

Host Decoder SDRAM data mask enable(Lower)

HD_M_DQMU

Host Decoder SDRAM data mask enable(Upper)

HD_M_RASN

Host Decoder SDRAM row address strobe

HD_M_WEN

Host Decoder SDRAM write enable

HSOUT

Horizontal synchronisation OUT

ION

Inverted ON: Enable the power supply for the digital board

when LOW

IRESET_DIG

Initialisation of the digital board, HIGH when power ON

JTAG3_TCK

JTAG Test Clock

JTAG3_TD_VIP_TO_VE

JTAG Transmitted Data Video Input Processor to Video

Encoder

JTAG3_TD_VSM_TO_VIP

JTAG Transmitted Data Versatile Stream Manager to Video

Input Processor

JTAG3_TMS

JTAG Test Mode Select

JTAG3_TRSTN

JTAG Test part ResetN

LOAD_DVN

LOAD Digital Video(LOW active)

MUTEN

Mute enable

MUTEN_LV

Mute enable Low Voltage

P_SCAN_YUV(7:0)

Progressive Scan digital video bus

R_IN_VIP

Video Red input to Video Input Processor

R_OUT

Video Red output from Host Decoder

R_OUT_B

Filtered Red Video output from Host Decoder

RAS

Row Address Strobe

RESETN

Reset Host Decoder

RESETN_BE

System reset basic engine (buffered)

RESETN_DVIO

System reset Digital Video Input Output (buffered)

RESETN_VE

System reset Video Encoder

ROMH_CEN

Flash 2 chip enable

ROML_CEN

Flash 1 chip enable

RSTN_BE

Reset control of basic engine

RSTN_DVIO

Reset control of DVIO

RTS1P

Ready To Send data to service serial interface

RX1P

Receive data from service serial interface

SCL

I2C bus clock

SD_CASN

SDRAM Column Address strobe output (active LOW)

SD_CLK

SDRAM clock output

SD_CLKE

SDRAM clock enable output

SD_CSN

SDRAM

SD_DQM(1:0)

SDRAM data mask enable output

Содержание DVDR880/001

Страница 45: ...Mechanical Instructions EN 47 DVDR880 890 0X1 4 4 2 Exploded View of the Set Figure 4 11 TR 01002_001 080502 ...

Страница 48: ...Mechanical Instructions EN 50 DVDR880 890 0X1 4 4 5 Dismantling Instructions Figure 4 14 ...

Страница 96: ...EN 98 DVDR880 890 0X1 7 Circuit Diagrams and PWB Layouts Layout Front Connector Panel FC TR 01030_001 150502 ...

Страница 107: ...Circuit Diagrams and PWB Layouts EN 109 DVDR880 890 0X1 7 Layout Analog Board Top View TR 01045_001 150502 ...

Страница 108: ...EN 110 DVDR880 890 0X1 7 Circuit Diagrams and PWB Layouts Layout Analog Board Overview Bottom View TR 01046_001 150502 ...

Страница 109: ...Circuit Diagrams and PWB Layouts EN 111 DVDR880 890 0X1 7 Layout Analog Board Part 1 Bottom View TR 01047_001 150502 ...

Страница 110: ...EN 112 DVDR880 890 0X1 7 Circuit Diagrams and PWB Layouts Layout Analog Board Part 2 Bottom View TR 01048_001 150502 ...

Страница 111: ...Circuit Diagrams and PWB Layouts EN 113 DVDR880 890 0X1 7 Test points overview Analog Board TR 01061_001 230502 ...

Страница 115: ...Circuit Diagrams and PWB Layouts EN 117 DVDR880 890 0X1 7 Tests points overview UPC12 Sub PCB TR 01053_001 140502 ...

Страница 165: ...Circuit IC Descriptions and List of Abbreviations EN 167 DVDR880 890 0X1 9 9 7 IC s Display Panel 9 7 1 IC7100 ...

Страница 166: ...Circuit IC Descriptions and List of Abbreviations EN 168 DVDR880 890 0X1 9 ...

Страница 167: ...Circuit IC Descriptions and List of Abbreviations EN 169 DVDR880 890 0X1 9 ...

Страница 174: ...Circuit IC Descriptions and List of Abbreviations EN 176 DVDR880 890 0X1 9 IC7411 ...

Страница 177: ...Circuit IC Descriptions and List of Abbreviations EN 179 DVDR880 890 0X1 9 9 9 IC sUPC12 Sub PCB 9 9 1 IC7825 ...

Страница 182: ...Circuit IC Descriptions and List of Abbreviations EN 184 DVDR880 890 0X1 9 ...

Страница 183: ...Circuit IC Descriptions and List of Abbreviations EN 185 DVDR880 890 0X1 9 ...

Страница 184: ...Circuit IC Descriptions and List of Abbreviations EN 186 DVDR880 890 0X1 9 ...

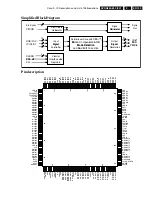

Страница 202: ...Circuit IC Descriptions and List of Abbreviations EN 204 DVDR880 890 0X1 9 9 11 IC s Divio Board 9 11 1 IC7404 NW700 ...

Страница 203: ...Circuit IC Descriptions and List of Abbreviations EN 205 DVDR880 890 0X1 9 ...