Peritek

6-4

Troubleshooting

Memory Map Example

In the following paragraphs the addresses given are based on the Motorola

167. This high performance Single Board Computer (SBC) has a 68040,

serial and parallel I/O, memory, SCSI, and Ethernet. Its specifications are

similar to SBCs made by Themis, Force, and Heurikon.

The Motorola 142/167/187/188/197 memory maps are programmed in the

debugger (using the ENV command) for A24, A32, D16, and D32

functions. Contact Peritek for more information. The CPU's have an

undocumented register which responds at offset 10 in A16 space, so

Peritek boards cannot use the bottom of A16 space. Also, the 167/187 may

be configured by operating system software to support only A16/D16

transfers. The Peritek device driver writes the correct value in VMEchip2.

The graphics board CSR block and 1 KB Line Buffer both reside in A16

space. The CSR block base address is controlled by 4 jumpers (see Section

II.4.1), which give 16 possible address offsets within the A16 space.

Normally, the offset is C000, giving a MVME CPU address of FFFFC000

for the CSR block. Now, the Line Buffer has an address offset determined

by a programmable register in the CSR block. These bits correspond to

address lines 10-15 for A16 and lines 10-23 for A24. On the MVME

CPU's, Peritek uses is 8000, giving a CPU address of FFFF8000 for A16.

The graphics board also can respond to a 64 MB window in A32 space,

giving access to the entire on-board memory. In this case, a programmable

register in the CSR block allows you program the address of that window.

The 6 bits in this register correspond to the high 6 bits of the A32 address.

In the MVME CPU, A32 space extends up to MVME CPU address

F0000000. Normally, we place the board at A0000000.

It is important to remember that the addresses which the graphics board

responds to are a function of the VMEbus address and the address

modifier codes. The address modifier codes must be asserted such that the

board's CSR group and Line Buffer spaces are in A16 space and the

extended memory block appears in A32 space. Not surprisingly, the

address modifier codes are set up by the CPU board's bus controller.

The graphics board responds to D8, D16 and D32 accesses in A16 space

and D8, D16, and D32 accesses in A32 space. However, bytes 0 and 1

(bits 16-31) are undefined for D32 accesses to the CSR block. Byte (D8)

writes to the CSR block have no effect; only D16 and D32 writes will

change these registers. Byte reads, however, do return the correct data.

Содержание VCD-V

Страница 2: ...Peritek ...

Страница 3: ...Peritek ...

Страница 5: ...Peritek ...

Страница 6: ...Peritek ...

Страница 10: ...Peritek ...

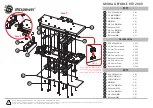

Страница 41: ...Peritek 2 10 Installing Your Peritek Graphics Board Figure 2 2 Jumper Locations for the VCT V and VCU V ...

Страница 42: ...Peritek Installing Your Peritek Graphics Board 2 11 Figure 2 3 Jumper Locations for the VCD V ...

Страница 94: ...Peritek Theory of Operation 4 15 Figure 4 1 VCD V Block Diagram ...

Страница 95: ...Peritek 4 16 Theory of Operation Figure 4 2 VCU V Block Diagram ...

Страница 96: ...Peritek Theory of Operation 4 17 Figure 4 3 VCT V Block Diagram ...